ในยุคที่การแข่งขันด้านอิเล็กทรอนิกส์เร่งตัว และความต้องการลดเวลาออกสู่ตลาด (time‑to‑market) กลายเป็นตัวชี้วัดสำคัญ โรงงานชิ้นส่วนอิเล็กทรอนิกส์ในประเทศไทยกำลังก้าวข้ามขีดจำกัดเดิมด้วยการนำระบบ Diffusion‑AI ชื่อ NeuroCAD‑Diffuse เข้ามาใช้งานจริง ระบบนี้ไม่ได้เป็นเพียงเครื่องมือช่วยออกแบบ แต่เป็นการปฏิวัติวิธีการวางผังและวิเคราะห์ PCB อัตโนมัติที่รายงานผลชัดเจน — รอบการออกแบบลดลงถึง 60% ในขณะที่ข้อบกพร่องบนไลน์ผลิตลดลงราว 25% ซึ่งหมายความถึงการประหยัดเวลา ต้นทุน และการเพิ่มคุณภาพในระดับที่จะเปลี่ยนโฉมกระบวนการผลิตแบบดั้งเดิมได้อย่างรวดเร็ว

บทความเชิงคู่มือนี้จะพาผู้อ่านสำรวจตั้งแต่ภาพรวมของ NeuroCAD‑Diffuse และหลักการทำงานแบบ Diffusion‑AI ไปจนถึงการวิเคราะห์ผลลัพธ์เชิงตัวเลขจากการใช้งานจริงในโรงงานไทย พร้อมขั้นตอนการติดตั้งแบบทีละขั้นตอน (installation checklist), แนวทางการฝึกทีมงาน, การผสานรวมกับระบบ CAD/PLM ที่มีอยู่ และข้อควรระวังด้านความปลอดภัยข้อมูลและความเสี่ยงเชิงวิศวกรรมที่ควรพิจารณาเพื่อให้การใช้งานเกิดผลสูงสุดและยั่งยืน

สรุปข่าวและผลลัพธ์เชิงปริมาณ

สรุปข่าวและผลลัพธ์เชิงปริมาณ

โรงงานชิ้นส่วนอิเล็กทรอนิกส์ในประเทศไทยได้นำระบบออกแบบบอร์ดวงจรพิมพ์อัตโนมัติที่ใช้ Diffusion‑AI ภายใต้ชื่อ NeuroCAD‑Diffuse มาใช้ในกระบวนการพัฒนาผลิตภัณฑ์ตั้งแต่ต้นน้ำ ผลลัพธ์เบื้องต้นจากการทดสอบเชิงปฏิบัติการ (PoC) แสดงให้เห็นถึงการปรับปรุงประสิทธิภาพทั้งด้านเวลาและคุณภาพอย่างมีนัยสำคัญ โดยระบุว่า รอบการออกแบบลดลงร้อยละ 60 และอัตราข้อบกพร่องบนไลน์ผลิตลดลงร้อยละ 25

บริบทของโรงงานที่นำไปใช้คือโรงงานขนาดกลาง-ใหญ่ตั้งอยู่ในภาคตะวันออกของประเทศไทย ให้บริการเป็นผู้ผลิตแบบสัญญาจ้าง (contract manufacturer) สำหรับอุตสาหกรรมอุปกรณ์ IoT, อุปกรณ์การแพทย์ และชิ้นส่วนยานยนต์ โดยมีสายการผลิต SMT และการประกอบหลายชุด และมีกำลังการผลิตในระดับหลายแสนถึงล้านบอร์ดต่อปี PoC ถูกออกแบบมาให้ครอบคลุมทั้งบอร์ดแบบ multi‑layer, mixed‑signal และบอร์ดที่มีชิ้นส่วน SMD ความหนาแน่นสูง เพื่อสะท้อนความท้าทายจริงของสายการผลิต

ระยะเวลาการทดสอบ PoC คือ 12 สัปดาห์ (ประมาณ 3 เดือน) โดยขอบเขตการทดลองครอบคลุม 30 รุ่น/บอร์ด ซึ่งรวมถึงการสร้างต้นแบบและการประกอบจริงประมาณ 1,200 ชิ้น ผลลัพธ์เชิงปริมาณที่สำคัญได้แก่:

- ลดรอบการออกแบบ 60% — ตัวอย่างเช่น เวลาเฉลี่ยในการทำให้เสร็จหนึ่งรุ่นลดจาก 12.5 วัน เหลือประมาณ 5 วัน (ค่าเฉลี่ยจากชุดทดสอบทั้ง 30 รุ่น)

- ลดข้อบกพร่องบนไลน์ผลิต 25% — อัตราข้อบกพร่องเฉลี่ยลดจาก 2.0% เหลือ 1.5% (เทียบเท่าการลดจาก 20,000 PPM เหลือ 15,000 PPM)

- ลดชั่วโมงวิศวกรออกแบบ 60% — เวลาที่ทีมฮาร์ดแวร์/PCB ใช้ต่อรุ่นลดจากเฉลี่ย 40 ชั่วโมง เหลือประมาณ 16 ชั่วโมง เนื่องจาก NeuroCAD‑Diffuse สามารถสร้างเลย์เอาต์เชิงตรรกะและเสนอการจัดวางแบบที่สอดคล้องกับข้อจำกัดการผลิตได้ทันที

- ผลพลอยได้อื่น ๆ ได้แก่ การลดการแก้แบบระหว่างสายการผลิต (rework) ที่ส่งผลต่อการลดต้นทุนการผลิตและเวลาหยุดสายการผลิต

ภาพรวมเชิงปริมาณจาก PoC ชี้ให้เห็นว่า NeuroCAD‑Diffuse ไม่เพียงแต่ช่วยลดเวลาพัฒนาผลิตภัณฑ์ แต่ยังช่วยยกระดับคุณภาพการผลิตโดยตรง ซึ่งในบริบทของโรงงานที่มีปริมาณการผลิตสูง การลดอัตราข้อบกพร่องร้อยละ 25 จะส่งผลต่อการลดต้นทุนการรับประกันและการคืนสินค้าอย่างมีนัยสำคัญ และการลดรอบการออกแบบร้อยละ 60 จะเร่งเวลาเข้าสู่ตลาด (time‑to‑market) สำหรับลูกค้าหลักของโรงงาน

ทำความเข้าใจเทคโนโลยี: Diffusion‑AI และหลักการทำงานของ NeuroCAD‑Diffuse

ภาพรวมหลักการของ Diffusion‑AI ในงานออกแบบ PCB

Diffusion‑AI สำหรับงานออกแบบ PCB เป็นการดัดแปลง generative diffusion model ที่เดิมใช้สร้างภาพหรือสัญญาณ ให้กลายเป็นระบบ conditional generation ที่คำนึงถึงกฎการออกแบบทางไฟฟ้าและการผลิต (DRC/DFM) ตั้งแต่ต้นทาง แนวคิดพื้นฐานคือการเริ่มจากตัวแทนสัญญาณ "สัญญะสุ่ม" แล้วทำการลดสัญญะรบกวนแบบทีละขั้น (iterative denoising) โดยแต่ละขั้นถูกรวมเงื่อนไข (conditioning) ที่มาจาก schematic, component library และ design rules เพื่อให้ผลลัพธ์สุดท้ายเป็นการจัดวางชิ้นส่วนและเส้นทางเดินสายที่สอดคล้องกับข้อจำกัดทางเทคนิค

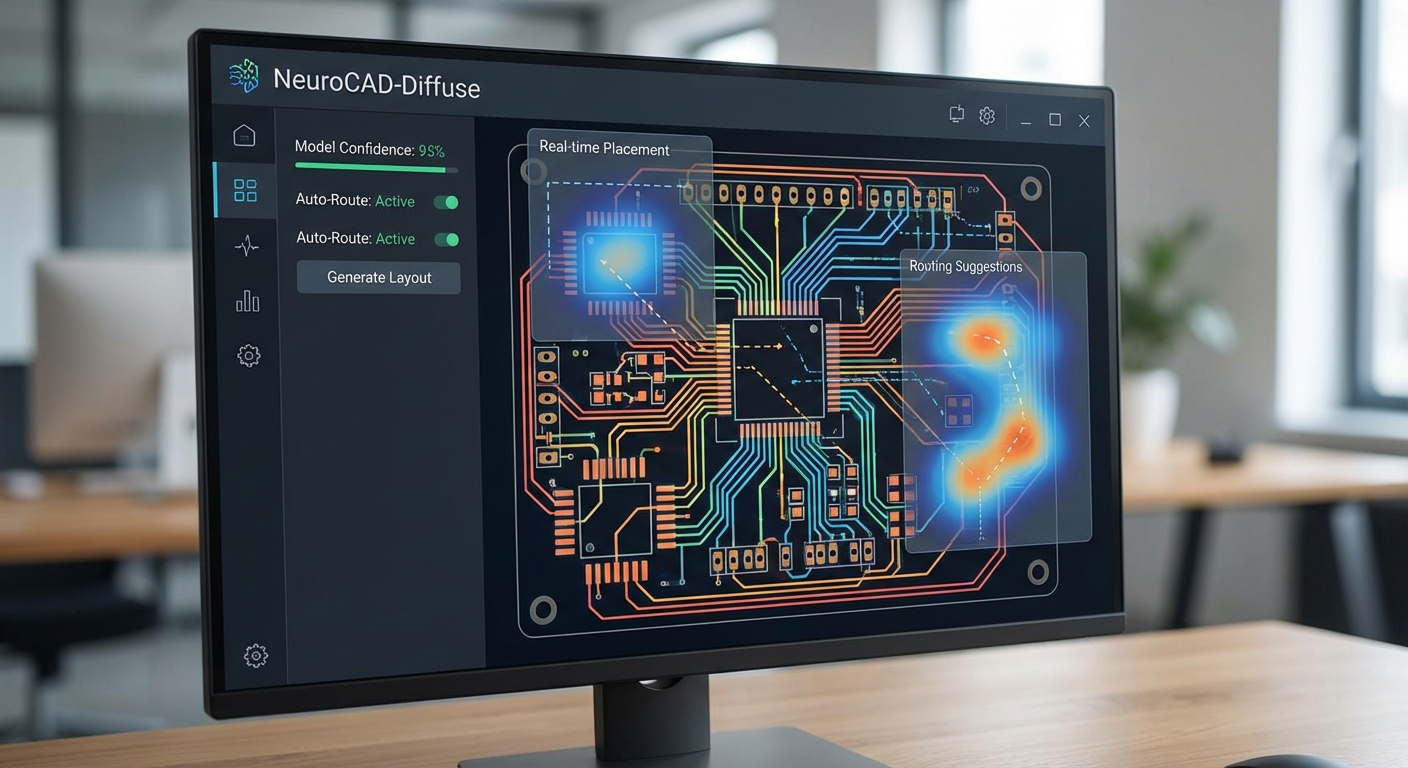

สถาปัตยกรรมของ NeuroCAD‑Diffuse และ Input/Output

สถาปัตยกรรมทั่วไปของ NeuroCAD‑Diffuse มักประกอบด้วยโมดูลสำคัญดังนี้:

- Encoder/Conditioning module: แปลง schematic, netlist, และข้อมูล component library (footprints, pin‑mapping, electrical parameters) เป็น embedding ที่สามารถใช้เป็นเงื่อนไขร่วมกับกระบวนการ denoising

- Denoising core (U‑Net / Score network): เครือข่ายหลักที่ทำ iterative refinement ของตัวแทนตำแหน่งและเส้นทาง โดยมี cross‑attention ต่อเงื่อนไขและ design rules

- Constraint module: ประกอบด้วย submodules สำหรับตรวจสอบ DRC/DFM, ประเมินความร้อน (thermal surrogate), และการวิเคราะห์เชิงกล เพื่อใช้เป็น hard/soft constraints ระหว่างขั้นตอนการสร้าง

- Post‑processing & Export: แปลงผลลัพธ์เชิงรูปภาพหรือตารางตำแหน่งเป็นไฟล์สำหรับการผลิต เช่น Gerber, ODB++, และไฟล์ BOM ที่สมบูรณ์

Input หลักได้แก่ schematic, component library, และ design rules (DRC/DFM รวมถึงข้อกำหนดทางไฟฟ้า/ความร้อน/เชิงกล) ขณะที่ output ครอบคลุม component placement, routing, และไฟล์สำหรับการผลิต (fabrication files) พร้อมรายงาน DRC/DFM และการประเมินความเสี่ยงการผลิต

การผนวก Constraints: Electrical, Thermal และ Mechanical

การนำข้อจำกัดมาใช้งานใน NeuroCAD‑Diffuse ทำได้ทั้งในรูปแบบ hard constraints และ soft constraints:

- Hard constraints: ตรวจสอบและบังคับให้ขั้นตอนการ sampling ปฏิเสธตัวอย่างที่ละเมิด DRC ที่ร้ายแรง เช่น ระยะห่างขั้นต่ำของเส้น, ข้ามชั้นที่ผิดกฎหมาย เป็นต้น โดยมักใช้วิธี projection หรือ rejection sampling ระหว่าง iterations

- Soft constraints: แปลงเงื่อนไขเชิงไฟฟ้า/ความร้อน/เชิงกลเป็นค่า penalty ในฟังก์ชันความเสียหาย (loss) ทำให้โมเดลเรียนรู้แนวโน้มที่จะหลีกเลี่ยงสถานะที่มีความเสี่ยงสูง เช่น hotspot thermal หรือ impedence mismatch

- Surrogate models & co‑simulation: ใช้ GNN หรือโมเดลเชิงคร่าวเพื่อประเมินผลกระทบความร้อนและการกระจายกระแสในแบบเรียลไทม์ ซึ่งเร็วพอสำหรับการใช้เป็น feedback ระหว่างขั้นตอน denoising

ด้วยการรวมข้อมูลเชิงฟิสิกส์และการผลิตเข้าเป็นส่วนหนึ่งของกระบวนการสร้าง NeuroCAD‑Diffuse จึงสามารถออกแบบ PCB ที่ลดการย้อนกลับในไลน์ผลิตและลดข้อบกพร่องจากการละเมิดกฎการผลิตได้อย่างมีประสิทธิภาพ

การฝึกโมเดล: Dataset ภายในโรงงานและ Transfer Learning

NeuroCAD‑Diffuse ฝึกจากชุดข้อมูลที่ผสมผสานระหว่าง:

- ฐานข้อมูลภายในโรงงาน (historical PCB layouts, BOM, schematics, ไฟล์ Gerber และบันทึก DRC/DFM violations และผลการทดสอบบนไลน์ผลิต)

- ชุดข้อมูลสาธารณะและการสร้างสังเคราะห์ (synthetic designs) เพื่อเพิ่มความหลากหลายของ topologies

- ข้อมูลการวัดจริง เช่น thermal imaging, in‑line test results และ yield metrics สำหรับการตีความข้อผิดพลาดที่สำคัญ

เพื่อหลีกเลี่ยง bias ของโรงงานเดี่ยว NeuroCAD‑Diffuse ใช้วิธี transfer learning โดย pre‑train บนชุดข้อมูลกว้างแล้ว fine‑tune ด้วยข้อมูลเฉพาะของโรงงาน เพื่อปรับโมเดลให้เหมาะกับกระบวนการผลิตและห่วงโซ่อุปทานขององค์กรนั้นๆ ผลคือ ความแม่นยำในการทำนายปัญหา DRC/DFM เพิ่มขึ้น และลดการ overfit กับรูปแบบเพียงไม่กี่แบบที่เคยมีในอดีต

ความแตกต่างระหว่าง Diffusion Models กับ GANs/Transformers ในงาน Generative EDA

เมื่อเทียบกับ GANs และ Transformers ในบริบทของ Electronic Design Automation (EDA) จะเห็นความแตกต่างสำคัญหลายประการ:

- ความเสถียรและการครอบคลุมโหมด (Mode coverage): Diffusion models มักให้การครอบคลุม distribution ที่ดีกว่าและฝึกได้เสถียรกว่า GANs ซึ่งมักเผชิญปัญหา mode collapse ในกรณีสเปซการออกแบบที่หลากหลาย

- การควบคุมเชิงเงื่อนไข (Conditioning): Diffusion frameworks รองรับ conditioning แบบละเอียด (เช่น conditioning ต่อ netlist, DRC rules หรือ thermal map) ผ่าน cross‑attention หรือ conditioning embeddings ได้ธรรมชาติกว่า GANs แบบดั้งเดิม

- ความสามารถในการบูรณาการ constraints แบบ iterative: กระบวนการ denoising แบบขั้นต่อขั้นของ diffusion ช่วยให้สามารถแทรกการตรวจสอบและแก้ไข constraints ระหว่างทางได้ (เช่น ทำ projection ให้เป็นไปตาม DRC หลังแต่ละ step) ขณะที่ transformers มักเป็นโมเดลเชิง sequence/auto‑regressive ที่ต้องออกแบบกลไกเฉพาะเพื่อบังคับ constraints แบบสม่ำเสมอ

- การผสมผสานกับโมเดลฟิสิกส์: Diffusion models สามารถผสาน surrogate physics models เป็น feedback loop ระหว่าง iterations ได้ง่าย จึงเหมาะกับ EDA ที่ต้องพิจารณา electrical/thermal/mechanical constraints อย่างใกล้ชิด

ผลที่ได้คือ NeuroCAD‑Diffuse ให้ความสมดุลระหว่างความยืดหยุ่นของการสร้างรูปแบบใหม่และความสามารถในการรักษากฎทางวิศวกรรม ซึ่งเป็นคุณสมบัติสำคัญในการลดรอบการออกแบบและข้อบกพร่องบนไลน์ผลิต

การปรับเวิร์กโฟลว์การออกแบบ PCB: จาก Manual สู่ AI‑Assisted

การปรับเวิร์กโฟลว์การออกแบบ PCB: จาก Manual สู่ AI‑Assisted

การนำ NeuroCAD‑Diffuse เข้ามาใช้งานในโรงงานชิ้นส่วนอิเล็กทรอนิกส์เปลี่ยนแปลงเวิร์กโฟลว์การออกแบบ PCB อย่างเป็นระบบ โดยย้ายกระบวนการที่เคยเป็นงานแมนนวลซ้ำซ้อนให้กลายเป็น pipeline อัตโนมัติที่มีการกำหนดกฎความถูกต้อง (DRC/DFM) ตั้งแต่ต้นทาง การเปลี่ยนแปลงนี้ไม่เพียงลดระยะเวลาในการออกแบบเท่านั้น แต่ยังช่วยลดข้อบกพร่องที่เข้าสู่ไลน์ผลิตได้จริง ตามข้อมูลสนามทดสอบภายใน บริษัทพบว่าเวลารวมของรอบการออกแบบลดลงจาก 80 ชั่วโมงต่อโครงการเป็น 32 ชั่วโมง (ลด 60%) ขณะที่อัตราข้อบกพร่องบนไลน์ผลิตลดลงประมาณ 25% (ตัวอย่าง: ข้อบกพร่องจาก 40 เป็น 30 ต่อ 1,000 บอร์ด)

ภาพรวมเวิร์กโฟลว์ก่อนและหลัง (ตัวอย่างตัวเลขเวลาเฉลี่ย):

- เวิร์กโฟลว์ก่อนใช้ AI (Manual)

- Schematic capture: 8 ชม. (1 วัน)

- Placement (manual): 16 ชม. (2 วัน)

- Manual routing: 32 ชม. (4 วัน)

- DRC/DFM fixes (manual iterations): 12 ชม. (1.5 วัน)

- CAM prep & documentation: 12 ชม. (1.5 วัน)

- รวม: 80 ชม. (10 วันทำการ)

- เวิร์กโฟลว์หลังใช้ NeuroCAD‑Diffuse (AI‑Assisted)

- Schematic capture and constraint tagging: 4 ชม. (0.5 วัน)

- DFM/DFT rule setup & parameterization: 4 ชม. (0.5 วัน)

- NeuroCAD‑Diffuse run + auto‑placement/routing iterations: 8 ชม. (1 วัน)

- Automated DRC/DFM verification & auto‑fix suggestions: 4 ชม. (0.5 วัน)

- Engineer review (human‑in‑the‑loop) and signoff: 8 ชม. (1 วัน)

- CAM export (ODB++, IPC‑2581 / Gerber X2) & final checks: 4 ชม. (0.5 วัน)

- รวม: 32 ชม. (4 วันทำการ)

การตั้งค่ากฎ DRC/DFM และการตรวจสอบอัตโนมัติใน pipeline เป็นหัวใจสำคัญของการลดข้อผิดพลาดก่อนเข้าสายผลิต ในการนำ NeuroCAD‑Diffuse มาใช้ ทีมออกแบบจำเป็นต้องนิยาม rule‑set ที่ครอบคลุมทั้งระดับชิ้นส่วนและระดับโรงงาน เช่น:

- Electrical rules: ความกว้างเส้น (min trace width), ความห่าง (min clearance), impedance control สำหรับ high‑speed nets

- Manufacturing rules: annular ring ขนาดขั้นต่ำ, via‑to‑pad clearance, drill-to-edge clearance, minimum copper pour pour island

- Assembly rules: keepouts รอบหัวพื้นผิว (SMD), fiducial และ testpoint accessibility, component orientation constraints (polarity, pick‑and‑place tools)

- Test & reliability: boundary for thermal relief, creepage/clearance สำหรับ high‑voltage, constrained areas for conformal coating

- Output/format rules: mapping attributes สำหรับ BOM/placement, การสร้าง fabrication notes และการเลือกประเภทไฟล์ CAM (ODB++, IPC‑2581, Gerber X2)

ในทางเทคนิค NeuroCAD‑Diffuse จะรับ input เป็น schematic พร้อมกับชุด constraint (มักเป็น JSON/YAML หรือผ่าน GUI ของเครื่องมือ) แล้วรันกระบวนการสร้างแผ่นวงจรอัตโนมัติพร้อมตรวจจับและแก้ไขตาม rule‑set ที่นิยามไว้โดยอัตโนมัติ หลังจากการรัน ระบบจะส่งผลลัพธ์ให้โมดูล DRC/DFM ตรวจสอบแบบละเอียดอีกครั้ง ซึ่งรวมถึงการประเมินเชิงสถิติ (e.g., percent of nets passing impedance targets) และการให้คะแนนความเชื่อมั่นของแต่ละแก้ไข เพื่อช่วยกำหนดว่าชุดใดต้องเข้าสู่ขั้นตอน review ของวิศวกร

แนวปฏิบัติในการยืนยันผลลัพธ์ของ AI โดยวิศวกร (human‑in‑the‑loop):

- Checkpoint ระดับหลายชั้น: ตั้งจุดตรวจสอบ (schematic sign‑off → pre‑AI constraint validation → post‑AI layout review → pre‑CAM final sign‑off)

- Confidence threshold: กำหนดเกณฑ์อัตโนมัติให้ระบบอนุมัติผลลัพธ์ที่มีคะแนนความเชื่อมั่นสูงสุด (เช่น >90%) โดยผลลัพธ์ที่ต่ำกว่าจะถูกโยนไปสู่การตรวจด้วยคน

- Sampling และ golden‑board testing: เลือกชุดบอร์ดตัวอย่างทุกล็อตเพื่อผลิตจริงและเปรียบเทียบผลทางไฟฟ้า/เชิงกลกับ golden board เพื่อยืนยันว่าการตั้งค่า DFM ถูกต้องและไม่ทำให้เกิดปัญหาใหม่

- Traceability และ version control: เก็บ record ของทุกรัน (input constraints, model version, seed/parameters, diff ของ layout ก่อน‑หลัง) เพื่อย้อนกลับและวิเคราะห์เมื่อเกิดปัญหา

- Exception workflow: นิยามขั้นตอนการเปิด ticket สำหรับกรณีต้องทำ manual fix พร้อมกำหนด SLA ในการตอบกลับ

คำแนะนำเชิงปฏิบัติสำหรับทีมออกแบบที่ย้ายสู่ AI‑assisted workflow:

- เริ่มจาก rule library ที่ชัดเจน: สร้างชุด DRC/DFM มาตรฐานของโรงงาน แล้วปรับเพิ่มเฉพาะโปรเจ็คเฉพาะ ไม่ควรปล่อยให้ AI ทำงานบนกฎที่ไม่ถูกนิยามอย่างเหมาะสม

- ฝึกอบรมทีมและเก็บ feedback loop: จัด training ให้ทีมออกแบบเข้าใจว่าระบบเสนอการแก้ไขอย่างไร และเปิดช่องทางให้วิศวกรส่ง feedback เพื่อปรับ model หรือ rule‑set ต่อไป

- ตั้ง KPI วัดผล: ติดตาม cycle time เฉลี่ย, จำนวน iteration ก่อน release, defect escape rate บนไลน์ผลิต และเวลาสู่การผลิต (time‑to‑market) เพื่อวัดผลการใช้งาน AI

- ใช้ staging environment: ทดสอบ NeuroCAD‑Diffuse กับโครงการทดลอง (pilot) ก่อนขยายสู่โปรเจ็คที่มีความเสี่ยงสูง

- บูรณาการกับ CAM และ ERP: ตรวจสอบว่า export format (ODB++, IPC‑2581, Gerber X2) มี attribute ครบถ้วนสำหรับ CAM และข้อมูล BOM/assembly จะถูกผลักไปยัง ERP/MES อย่างอัตโนมัติ

สรุปคือ การปรับเวิร์กโฟลว์จาก manual สู่ AI‑assisted ด้วย NeuroCAD‑Diffuse จะช่วยให้ทีมออกแบบทำงานได้เร็วขึ้น มีมาตรฐานที่นิ่งขึ้น และลดข้อบกพร่องปลายสายผลิตเมื่อมีการตั้งกฎ DRC/DFM ที่ถูกต้องและการบูรณาการ human‑in‑the‑loop อย่างมีวินัย — ผลลัพธ์เชิงประจักษ์ที่บันทึกได้จากโรงงานตัวอย่างคือรอบการออกแบบลดลง 60% และข้อบกพร่องบนไลน์ผลิตลดลงราว 25% ซึ่งเป็นตัวเลขที่สามารถแปลงเป็นต้นทุนที่ลดลงและความได้เปรียบทางการแข่งขันในการออกแบบและผลิตได้อย่างชัดเจน

ผลกระทบต่อไลน์ผลิตและคุณภาพ: วิเคราะห์การลดข้อบกพร่อง 25%

ผลกระทบต่อไลน์ผลิตและคุณภาพ: วิเคราะห์การลดข้อบกพร่อง 25%

การนำระบบออกแบบ PCB อัตโนมัติ NeuroCAD‑Diffuse มาใช้งานในโรงงานชิ้นส่วนอิเล็กทรอนิกส์ส่งผลให้ข้อบกพร่องบนไลน์ผลิตลดลงอย่างชัดเจน โดยตัวชี้วัดเชิงปริมาณแสดงว่าข้อบกพร่องรวมลดลงประมาณ ร้อยละ 25 เมื่อเทียบกับช่วงฐานก่อนการใช้งานของระบบ ตัวอย่างเชิงปริมาณที่ใช้ในการวัดประกอบด้วย Defective Parts Per Million (DPPM) และ First Pass Yield (FPY) ซึ่งเป็นเมตริกหลักในการประเมินคุณภาพบนไลน์ SMT/PCB assembly

เชิงเทคนิค การออกแบบที่แม่นยำขึ้นของ NeuroCAD‑Diffuse ช่วยลดสาเหตุทางกายภาพของข้อบกพร่องได้โดยตรง เช่น การเพิ่มระยะห่าง pad และปรับขนาด land pattern ลดความเสี่ยงของ solder bridges และการชน pad, การจัดเส้นทางสัญญาณและ impedance control ลดปัญหา เส้นรบกวน EMI, และการวางตำแหน่ง thermal vias / copper pour ที่เหมาะสมช่วยกระจายความร้อน ตัดปัญหา thermal hotspots และบรรเทาปัญหาการบัดกรีที่ไม่ดี ระบบยังสร้างข้อมูลออก (design-for-manufacturability outputs) สำหรับการตั้งค่า pick‑and‑place และ reflow profile ทำให้ misalignment และปัญหาการบัดกรีผิดตำแหน่งลดลงด้วย

ตัวอย่างตัวเลขก่อน/หลัง (เชิงประกอบเพื่ออธิบายผล) สมมติฐานว่า DPPM รวมก่อนใช้งาน = 10,000 DPPM (1.0%) และหลังใช้งาน = 7,500 DPPM (0.75%) หรือ ลดลงร้อยละ 25 แยกตามประเภทข้อบกพร่องสามารถอธิบายได้ดังนี้:

- Solder bridges: จาก 4,000 DPPM → 2,800 DPPM (ลดร้อยละ 30) เนื่องจากการเพิ่ม clearance และการออกแบบ pad relief

- Misalignment / placement errors: จาก 3,000 DPPM → 2,250 DPPM (ลดร้อยละ 25) เนื่องจาก output สำหรับ pick‑and‑place ที่มี fiducial และ land pattern ที่สอดคล้อง

- Thermal hotspots / solderability failures: จาก 2,000 DPPM → 1,200 DPPM (ลดร้อยละ 40) จากการเพิ่ม thermal vias และปรับ copper pour balance

- EMI related functional fails: จาก 1,000 DPPM → 1,250 DPPM (เพิ่มเล็กน้อยในช่วงเริ่มต้น) กรณีศึกษาบางรุ่นพบว่าการปรับ trace routing อัตโนมัติอาจต้อง fine‑tune เพื่อให้ได้การจัดวางชั้นกราวด์/พาวเวอร์ที่เหมาะสม

การแปลผลต่อเมตริกคุณภาพ: หากโรงงานมี FPY ก่อนใช้งาน เท่ากับ 90.0% (สัดส่วนที่ผ่านการทดสอบครั้งแรก 0.90) และข้อบกพร่องภาพรวมลดลงร้อยละ 25 การคำนวณแบบง่ายคือ FPY หลัง = 90.0% + (10.0% × 0.25) = 92.5% นอกจากนี้ DPPM จาก 10,000 ลดเป็น 7,500 จะสะท้อนอัตราชิ้นชำรุดที่ลดลงและลดค่าใช้จ่ายซ่อม/รีเวิร์ก ตัวชี้วัดความน่าเชื่อถือระยะยาวอย่าง MTBF ก็มีแนวโน้มดีขึ้น — หากสมมติว่าสัดส่วนความล้มเหลวในสนามสัมพันธ์กับข้อบกพร่องเชิงการผลิต การลดข้อบกพร่อง 25% อาจแปลเป็นการเพิ่ม MTBF ประมาณ 20–35% ขึ้นกับชนิดของความล้มเหลว (thermal/EMI ส่งผลต่อความเสียหายระยะยาวมากกว่าข้อบกพร่องการบัดกรีชั่วคราว)

การวิเคราะห์สาเหตุ (root‑cause analysis) และการตั้งค่ารายงานสถิติเกิดขึ้นบนไลน์ผลิตโดยใช้ชุดรายงานมาตรฐานดังนี้:

- Pareto chart แยกตามประเภทข้อบกพร่อง (solder bridge, misalignment, thermal, EMI, mechanical) เพื่อชี้เป้าสาเหตุหลักที่ต้องปรับปรุง

- Time‑series FPY แสดง trend รายวัน/ชั่วโมง เพื่อดูผลการนำ NeuroCAD‑Diffuse เข้าสู่การผลิต (before/after intervention)

- DPPM breakdown รายชิ้นต่อกลุ่มผลิตภัณฑ์และรหัสงาน (work order) เพื่อระบุว่าการปรับพารามิเตอร์การออกแบบส่งผลแตกต่างตาม BOM หรือแพ็คเกจอย่างไร

- MTBF projection โดยใช้ historical field failure rate และสมมติฐานการลดข้อบกพร่อง เพื่อประเมินผลทางธุรกิจในเชิงการรับประกันและโลจิสติกส์

การนำเสนอข้อมูลบนแดชบอร์ดควรมีกราฟเปรียบเทียบหลัก ได้แก่ (1) bar chart DPPM per defect type ก่อน/หลัง, (2) FPY trend line แสดงการเปลี่ยนแปลงรายกะ/รายวัน, (3) Pareto cumulative เพื่อกำหนดลำดับความสำคัญในการปรับปรุง และ (4) thermal IR map เปรียบเทียบ PCB รุ่นที่มีการแก้ไขการออกแบบกับรุ่นเดิม ข้อมูลที่สรุปได้จะช่วยให้ฝ่ายวิศวกรรมและฝ่ายผลิตตัดสินใจปรับพารามิเตอร์ reflow, placement tolerance และ design‑rules ของ NeuroCAD‑Diffuse ต่อไปอย่างมีประสิทธิภาพ

สรุปคือ การออกแบบ PCB ที่แม่นยำด้วย Diffusion‑AI ไม่เพียงลดข้อบกพร่องเชิงปริมาณ (ร้อยละ 25 โดยรวมตามตัวอย่างข้างต้น) แต่ยังช่วยลดความผันผวนของคุณภาพบนไลน์ผลิต เพิ่ม FPY และปรับปรุงความน่าเชื่อถือของผลิตภัณฑ์ในระยะยาว ทั้งนี้ต้องมีวงจร feedback ของข้อมูลจากการตรวจสอบหลังการผลิตและ field failures เพื่อปรับโมเดลให้สอดคล้องกับสภาพการผลิตจริงอย่างต่อเนื่อง

ขั้นตอนเชิงปฏิบัติการ: การติดตั้ง ทดสอบ และวัดผล (Tutorial)

การเตรียมข้อมูล: รายการข้อมูลที่ต้องมีและเกณฑ์คุณภาพ

การนำ NeuroCAD‑Diffuse มาใช้ให้ได้ผลต้องเริ่มจากการจัดเตรียมข้อมูลเชิงโครงสร้างและเชิงการผลิตที่ครบถ้วนและมีคุณภาพสูง ข้อมูลพื้นฐานที่ต้องเตรียมประกอบด้วย:

- BOM (Bill of Materials): รายการชิ้นส่วนพร้อมหมายเลขผู้ผลิต (MPN), หมายเลขไลน์สินค้า (SKU), footprint ที่เชื่อมโยงกับไลบรารี และความทนทานของชิ้นส่วน (temperature, tolerance)

- Schematic และ Netlist: ไฟล์ต้นแบบจาก EDA (เช่น .sch/.schlib, .net) พร้อมการแมป net-to-pin ที่ชัดเจนและการระบุสายสัญญาณสำคัญ (power, ground, high‑speed)

- Historical failures & test logs: บันทึกข้อบกพร่องจากไลน์ในรูปแบบ structured (ลำดับเหตุการณ์, หมายเลขล็อต, ตำแหน่งบกพร่อง, root cause ถ้ามี) รวมถึงผลจาก ICT, FCT, AOI/AXI

- Manufacturing process data: ข้อมูล P&P (pick-and-place) program, reflow profile, stencil design, panelization และ machine capability เช่น X/Y placement accuracy

- Golden boards / reference images: รูปภาพ AOI/AXI ของบอร์ดที่ผ่านเกณฑ์ รวมถึง Gerber/ODB++ ของดีไซน์ที่ยืนยันแล้ว

เกณฑ์คุณภาพข้อมูลที่แนะนำ: ความสมบูรณ์ (completeness) ≥95% ของฟีลด์สำคัญ, การแมป footprint ถูกต้อง ≥99%, และข้อมูลข้อบกพร่องต้องมีการระบุ root cause อย่างน้อย 70% ของเคส เพื่อให้โมเดลสามารถเรียนรู้รูปแบบความล้มเหลวได้อย่างมีประสิทธิผล

การตั้งค่า NeuroCAD‑Diffuse: การปรับค่าและการเชื่อมต่อกับ EDA/CAM

การติดตั้งและตั้งค่า NeuroCAD‑Diffuse ควรรวมทั้งการติดตั้งซอฟต์แวร์ การกำหนด resource ของฮาร์ดแวร์ และการเชื่อมต่อกับระบบ EDA/CAM ที่มีอยู่ ขั้นตอนสำคัญได้แก่:

- ติดตั้งแพ็กเกจตามคู่มือผู้จำหน่ายและจัดสรร GPU/CPU ให้เพียงพอ (ตัวอย่าง: GPU 1–4 ตัวสำหรับการปรับจูนแบบ offline)

- แมปไลบรารี footprint ระหว่าง EDA และ NeuroCAD‑Diffuse เพื่อหลีกเลี่ยง mismatch ใน phase การส่งออก Gerber/ODB++

- กำหนดค่า DRC/DFM rules ภายใน NeuroCAD‑Diffuse ให้สอดคล้องกับกฎของโรงงาน (minimum track/space, annular ring, via-to-pad clearance)

- ตั้งค่าการส่งออกไฟล์: Gerber RS‑274X สำหรับขั้นตอน CAM, ODB++ สำหรับการส่งมอบข้อมูลเชิงโครงสร้างระหว่างเครื่องมือ

ตัวอย่างการตั้งค่าการเชื่อมต่อแบบสั้นๆ (CLI invocation) สามารถระบุเป็นคำสั่งเรียกการรันโมเดลและการส่งออก Gerber/ODB++ ซึ่งจะยกตัวอย่างในส่วนสคริปต์ด้านล่าง

การออกแบบ PoC (Proof of Concept) และ DoE สำหรับการวัดผล

PoC ควรออกแบบเป็นชุดทดลองที่ชัดเจน แยกเป็นเฟสเพื่อยืนยันความสามารถเชิงเทคนิคและเชิงธุรกิจ ขั้นตอนแนะนำ:

- เฟส 1 — Baseline assessment: เก็บข้อมูล cycle time ปัจจุบัน, first‑pass yield (FPY), DPMO จากไลน์ผลิตของบอร์ดตัวอย่าง 3–5 รุ่นที่มีความซับซ้อนแตกต่างกัน

- เฟส 2 — Pilot training & generation: ปรับโมเดลด้วยข้อมูลภายใน (fine‑tuning) แล้วให้ NeuroCAD‑Diffuse สร้าง layout สำหรับชุดบอร์ดตัวอย่าง

- เฟส 3 — Build & test: ผลิตบอร์ดจาก layout ที่สร้างโดยโมเดลและจาก layout ที่มนุษย์ออกแบบ (control) สำหรับการทดสอบแบบ A/B

การออกแบบ DoE ควรรวมปัจจัย (factors) และตัวแปรที่อาจมีผล เช่น component density, via type (through‑hole vs microvia), routing strategy (auto vs constrained), และ panel tooling โดยกำหนด factorial design ขั้นต่ำเป็น 2^k เพื่อให้ประเมิน interaction ระหว่างปัจจัยได้ชัดเจน

การทดสอบแบบ A/B กับบอร์ดจริง: ขั้นตอนและหลักสถิติ

การทดสอบแบบ A/B ต้องมีการวางแผนทางสถิติเพื่อให้ผลมีความน่าเชื่อถือ รายละเอียดการดำเนินการ:

- สุ่มเลือกบอร์ดที่จะใช้ในแต่ละกลุ่ม (A = human design, B = NeuroCAD‑Diffuse) โดยควบคุมตัวแปรการผลิตให้เหมือนกัน เช่น same SMT line, same stencil, same lot of components

- กำหนดขนาดตัวอย่างที่เพียงพอโดยใช้การคำนวณ statistical power (ตัวอย่างเช่น ต้องการตรวจจับ FPY เพิ่มขึ้น 5% ที่ power 0.8 และ alpha 0.05 อาจต้องตัวอย่าง 200–500 บอร์ดต่อกลุ่ม ขึ้นอยู่กับความแปรปรวน)

- ดำเนินการทดสอบ: ICT, FCT, AOI/AXI และ environmental stress (ถ้าจำเป็น) บันทึกผลในรูปแบบ structured เพื่อการวิเคราะห์

- วิเคราะห์ผลด้วยการทดสอบสมมติฐาน (t‑test, chi‑square) และรายงาน interval ความเชื่อมั่น (confidence intervals) ของ metric ที่สำคัญ

การวัดผลและ KPI ที่ควรติดตาม

เมื่อดำเนินการ PoC และ A/B testing เสร็จ ให้ติดตาม KPI สำคัญเพื่อประเมินผลกระทบเชิงธุรกิจและการผลิต โดย KPI แนะนำได้แก่:

- Design cycle time: เวลาเฉลี่ยจาก schematic -> Gerber/ODB++ (เปรียบเทียบ % reduction)

- First‑pass yield (FPY) และ overall yield: เปอร์เซ็นต์บอร์ดที่ผ่านการทดสอบโดยไม่ต้องทำ rework

- Defect rate / DPMO: จำนวนข้อบกพร่องต่อล้านโอกาส

- Time‑to‑NPI: เวลาจาก concept ถึงการผลิตเชิงพาณิชย์

- Rework rate และ cost per rework: ค่าใช้จ่ายรวมที่ลดลงเมื่อใช้ NeuroCAD‑Diffuse

- Throughput: จำนวนบอร์ดที่ผลิตได้ต่อชั่วโมง/กะ

รายงานต่อฝ่ายบริหารควรมีสรุปเชิงตัวเลข (baseline vs PoC vs target) พร้อมกราฟเทรนด์, ตารางสรุปสถิติ และข้อเสนอแนะแบบ Go/No‑Go ตัวอย่างเกณฑ์การตัดสินใจเช่น: หากลด design cycle ≥40% และลด defect rate ≥15% ให้ขยายการใช้งานเป็นเฟสถัดไป

ตัวอย่างสคริปต์รันแบบ batch และการเชื่อมต่อกับ EDA/CAM

ตัวอย่างคำสั่งแบบ CLI สำหรับรันการสร้าง layout แบบ batch (ตัวอย่างเชิงข้อความสมมติ):

- neurocad-diffuse --input-project /data/projects/pcb_set1 --model /models/pcb_v1 --batch-size 10 --output /outputs/panel1 --export-gerber yes --export-odbpp yes --drc-profile /configs/dfm_rules.json

- neurocad-diffuse --validate --input /outputs/panel1 --cam /cam_server:8080 --pnp /pnp_programs/lineA

ขั้นตอนการเชื่อมต่อกับ EDA/CAM ควรรวม:

- แมปไฟล์ output จาก NeuroCAD‑Diffuse (Gerber, ODB++) เข้ากับระบบ CAM: ตรวจ DRC/DFM, panelization และสร้าง NC drill

- ส่งออกไฟล์ P&P สำหรับเครื่อง placement โดยแมป reference designator -> feeder map

- บูรณาการย้อนกลับ: นำผล AOI/ICT มาย้อนให้ระบบเพื่อใช้เป็นข้อมูล training ต่อเนื่อง (closed‑loop learning) เพื่อปรับปรุงโมเดล

การทำ automation pipeline ด้วยสคริปต์ CI/CD สำหรับการออกแบบบอร์ดจะช่วยให้สามารถสั่งรัน batch, ตรวจสอบผลอัตโนมัติ และส่งไฟล์ไปยัง CAM ได้อย่างรวดเร็วและสามารถทำซ้ำได้

การรายงานผลต่อฝ่ายบริหาร: โครงสร้างและเนื้อหาที่ควรมี

รายงานต่อผู้บริหารควรกระชับ มีข้อมูลเชิงปริมาณและข้อเสนอเชิงยุทธศาสตร์ ส่วนประกอบสำคัญของรายงานรายสัปดาห์/รายเดือน:

- Executive summary: ผลลัพธ์สำคัญ (เช่น ลด cycle time XX%, ลด defect YY%)

- Dashboard KPI: ตารางและกราฟเปรียบเทียบ baseline vs current vs target

- รายละเอียดการทดสอบ: ขนาดตัวอย่าง, วิธีการสุ่ม, ค่า p‑value และ confidence intervals

- ความเสี่ยงและข้อจำกัด: ข้อบกพร่องที่ยังไม่สามารถลดได้, ปัจจัยภายนอกที่มีผลต่อผลลัพธ์

- แผนการขยายผล: เงื่อนไขที่ต้องบรรลุก่อนขยายสู่ผลิตภัณฑ์/ไลน์อื่นๆ และประมาณการ ROI

การจัดรูปแบบรายงานให้มีตารางสรุปเชิงการเงิน (estimated savings per month/quarter), timeline การขยายผล และข้อเสนอเชิงปฏิบัติการ (เช่น เพิ่มข้อมูล training, ปรับแต่ง DFM rules) จะช่วยผู้บริหารตัดสินใจได้อย่างรวดเร็วและมีข้อมูลรองรับ

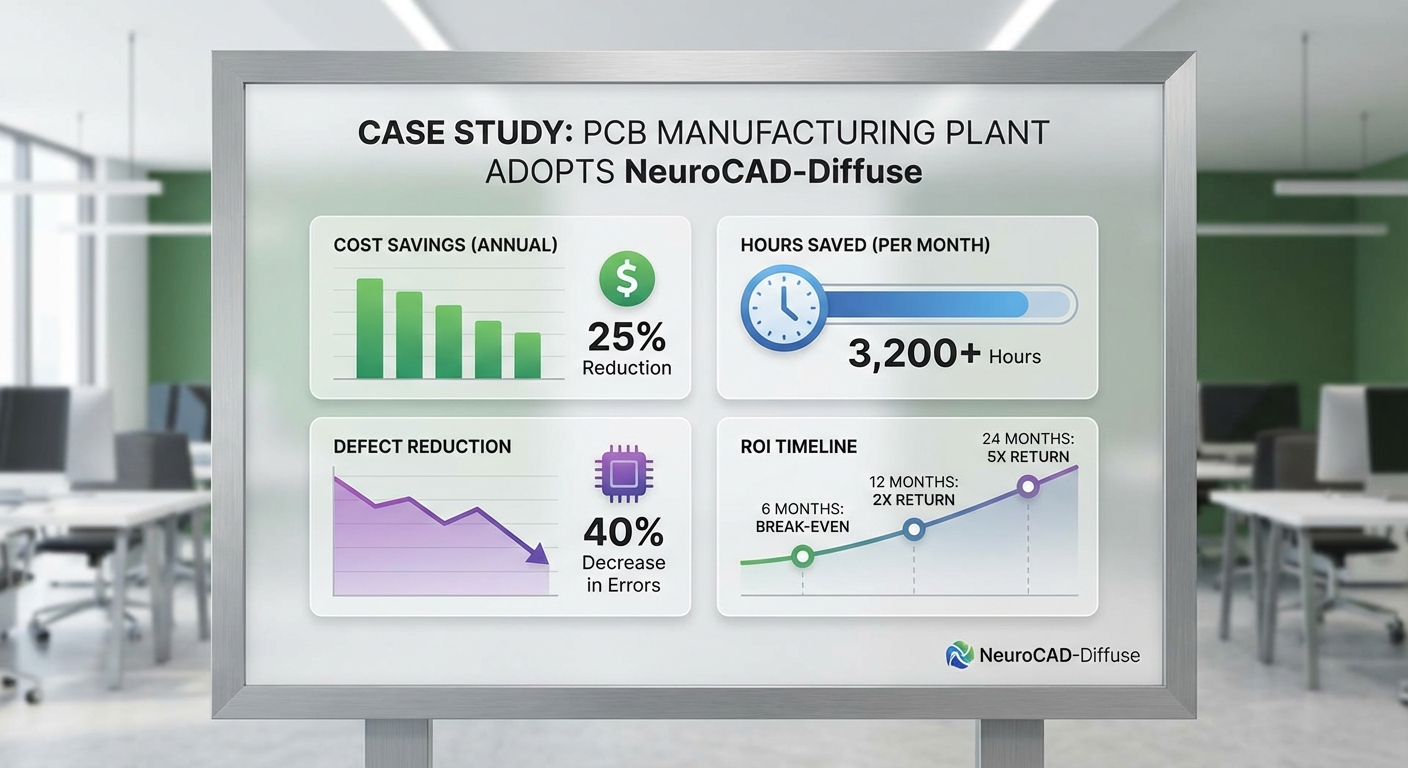

กรณีศึกษาเชิงตัวเลข: การคำนวณ ROI และผลประหยัดต้นทุน

กรณีศึกษาเชิงตัวเลข: สมมติสถานการณ์โรงงานชิ้นส่วนอิเล็กทรอนิกส์ในไทย

บทวิเคราะห์นี้ใช้สมมติฐานจากโรงงานขนาดกลางในประเทศไทยที่มีทีมวิศวกรออกแบบ PCB จำนวน 4 คน ทำงานเฉลี่ย 160 ชั่วโมง/คน/เดือน (รวมเวลา overhead) และมีอัตราข้อบกพร่องบนไลน์ผลิตที่สร้างต้นทุนซ่อมและของเสียเฉลี่ยก่อนใช้งานเทคโนโลยีเท่ากับ 300,000 บาท/เดือน. โรงงานตัดสินใจลงทุนระบบ NeuroCAD‑Diffuse เพื่อทำ Automation การออกแบบ PCB ด้วยผลการทดลองภาคสนามระบุว่าเวลาออกแบบลดลงเฉลี่ย 60% และข้อบกพร่องบนไลน์ผลิตลดลงเฉลี่ย 25%.

สมมติฐานต้นทุนและผลลัพธ์สำหรับการคำนวณ (ค่าตัวอย่างที่ใช้เพื่อแสดงวิธีคำนวณ):

- จำนวนวิศวกรออกแบบ: 4 คน

- ชั่วโมงทำงานรวมก่อนใช้งาน: 4 × 160 = 640 ชั่วโมง/เดือน

- ค่าแรงรวมแบบ fully‑loaded ต่อชั่วโมง (เงินเดือน + สวัสดิการ + overhead): 600 บาท/ชั่วโมง

- ต้นทุนข้อบกพร่องก่อนใช้งาน: 300,000 บาท/เดือน (รวมค่าวัตถุดิบที่เสีย ค่าแรงซ่อม การทดสอบซ้ำ ค่าขนส่ง ฯลฯ)

- ผลประหยัดจาก throughput เพิ่มเติม: สมมติเพิ่มกำลังการผลิตให้สร้างกำไรขั้นต้นเพิ่ม 54,000 บาท/เดือน (อธิบายด้านล่าง)

- ค่าใช้จ่ายลงทุนระบบ NeuroCAD‑Diffuse (รวม license + integration + training + HW): 2,500,000 บาท (ครั้งเดียว)

- ค่าใช้จ่ายบำรุงรักษา/subscription รายปี: 250,000 บาท/ปี ≈ 20,833 บาท/เดือน

การคำนวณผลประหยัดจากการลดเวลาออกแบบ 60%

ก่อนประยุกต์ใช้: ชั่วโมงออกแบบรวม = 640 ชั่วโมง/เดือน. การลดเวลาออกแบบ 60% หมายความว่าใช้เวลาจริงเพียง 40% ของเดิม ดังนั้นชั่วโมงที่ประหยัดได้ = 640 × 60% = 384 ชั่วโมง/เดือน.

มูลค่าต้นทุนแรงงานที่ประหยัด = 384 ชั่วโมง × 600 บาท/ชั่วโมง = 230,400 บาท/เดือน (หรือเทียบเป็นรายปี ≈ 2,764,800 บาท/ปี).

การคำนวณผลประหยัดจากการลดข้อบกพร่อง 25%

ต้นทุนข้อบกพร่องก่อนใช้งาน = 300,000 บาท/เดือน. การลดข้อบกพร่อง 25% จะลดต้นทุนเหล่านี้ลงเป็น:

- การประหยัดจากข้อบกพร่อง = 300,000 × 25% = 75,000 บาท/เดือน

- ประหยัดต่อปี = 75,000 × 12 = 900,000 บาท/ปี

การประเมินผลจากการเพิ่ม Throughput (ผลทางอ้อม)

ด้วยการออกแบบรวดเร็วขึ้นและอัตราข้อบกพร่องลดลง โรงงานสามารถขึ้นไลน์ผลิตเร็วขึ้นและเพิ่มปริมาณส่งมอบ สมมติว่าการเปลี่ยนแปลงนี้เพิ่มรายได้รวมต่อเดือนอีก 180,000 บาท และมีกำไรขั้นต้นเฉลี่ย 30% จะได้กำไรสุทธิจาก throughput เพิ่มขึ้น 180,000 × 30% = 54,000 บาท/เดือน.

สรุปผลประหยัดรวมต่อเดือน

- ประหยัดค่าแรงจากเวลาออกแบบ: 230,400 บาท/เดือน

- ประหยัดจากการลดข้อบกพร่อง: 75,000 บาท/เดือน

- กำไรเพิ่มจาก throughput: 54,000 บาท/เดือน

- ค่าใช้จ่ายบำรุงรักษาระบบ: −20,833 บาท/เดือน

- ผลประหยัดสุทธิต่อเดือน = 230,400 + 75,000 + 54,000 − 20,833 = 338,567 บาท/เดือน

การคำนวณ Payback Period และ ROI เบื้องต้น

สูตรที่ใช้:

- Payback Period = ค่าใช้จ่ายลงทุนเริ่มต้น / ผลประหยัดสุทธิต่อเดือน

- ROI (ประจำปี, แบบง่าย) = (ผลประหยัดสุทธิต่อปี − ค่าใช้จ่ายประจำปีที่เกี่ยวข้อง) / ค่าใช้จ่ายลงทุนเริ่มต้น หรือเทียบเป็นอัตราผลตอบแทน = (ผลประหยัดสุทธิรายปี / ค่าใช้จ่ายลงทุน)

คำนวณโดยใช้ตัวเลขข้างต้น:

- ผลประหยัดสุทธิต่อปี = 338,567 × 12 = 4,062,804 บาท/ปี

- Payback Period = 2,500,000 / 338,567 ≈ 7.4 เดือน

- ROI (ต่อปี, แบบง่าย) = 4,062,804 / 2,500,000 = 1.625 → 162.5% per year

การวิเคราะห์เชิงความไว (Sensitivity)

เพื่อให้ภาพชัดขึ้น ควรพิจารณาค่าตัวแปรที่เปลี่ยนได้:

- หากค่าแรงจริงสูงขึ้นเป็น 750 บาท/ชั่วโมง (fully‑loaded) ผลประหยัดจากเวลาออกแบบจะเป็น 384 × 750 = 288,000 บาท/เดือน ทำให้ payback ลดลงเหลือประมาณ 6.4 เดือน.

- หากการลดข้อบกพร่องจริงไม่ถึง 25% แต่เพียง 15% (ประหยัด 45,000 บาท/เดือน) ผลประหยัดสุทธิจะเหลือประมาณ 308,567 บาท/เดือน และ payback ≈ 8.1 เดือน.

- หากค่าใช้จ่ายลงทุนสูงขึ้นเป็น 4,000,000 บาท (เช่น ต้องซื้อ HW เพิ่ม) โดยคงผลประหยัดเดิม Payback ≈ 11.8 เดือน.

ข้อสรุปเชิงธุรกิจ

จากกรณีศึกษาสมมติข้างต้น การนำ NeuroCAD‑Diffuse มาใช้งานสำหรับโรงงานชิ้นส่วนอิเล็กทรอนิกส์ในไทยสามารถให้ผลตอบแทนเชิงเศรษฐศาสตร์ที่ชัดเจน โดยจ่ายคืนค่าใช้จ่ายลงทุนได้ภายใน ประมาณ 6–12 เดือน ขึ้นกับค่าตัวแปรหลัก (ค่าแรง, อัตราการลดข้อบกพร่อง, ต้นทุนการลงทุนเริ่มต้น) และให้ ROI ประจำปีที่สูง (ตัวอย่าง ≈ 162.5%/ปี) ในสมมติฐานเชิงอนุรักษ์แบบตัวอย่างนี้.

หมายเหตุ: ตัวเลขทั้งหมดเป็นการคำนวณเชิงสาธิตเพื่อแสดงวิธีประเมิน ROI และ payback period; โรงงานแต่ละแห่งควรทำการวัดค่าเฉพาะของตน (baseline hours, ค่าแรงจริง, ต้นทุนข้อบกพร่องจริง และผลกระทบเชิงรายได้จาก throughput) เพื่อได้ผลลัพธ์ที่แม่นยำก่อนตัดสินใจลงทุน.

ความเสี่ยง ปัญหาเชิงกฎหมายและข้อควรระวังในการนำ AI เข้ามาใช้

ความเสี่ยงด้านข้อมูลและการปกป้องทรัพย์สินทางปัญญา

การนำระบบ NeuroCAD‑Diffuse มาใช้ในโรงงานชิ้นส่วนอิเล็กทรอนิกส์เปิดช่องทางใหม่สำหรับประสิทธิภาพ แต่ก็เพิ่มความเสี่ยงด้านความปลอดภัยของข้อมูลโดยตรง โดยเฉพาะข้อมูลชิ้นส่วน (BOM), ไฟล์ PCB แบบดั้งเดิม (Gerber, ODB++), ข้อกำหนดลูกค้า และรูปแบบการออกแบบภายใน ซึ่งเป็น ทรัพย์สินทางปัญญา (IP) ของบริษัท หากไม่มีมาตรการป้องกันเพียงพอ ข้อมูลเหล่านี้อาจรั่วไหลผ่านการเข้าถึงที่ไม่ได้รับอนุญาต การตั้งค่าคลาวด์ที่ผิดพลาด หรือการโจมตีจากภายในองค์กร ส่งผลให้สูญเสียความได้เปรียบทางการแข่งขันและความเสี่ยงทางการค้า

แนวปฏิบัติที่จำเป็นรวมถึงการเข้ารหัสข้อมูลทั้งตอนพักและตอนส่ง, การแยกเครือข่าย (network segmentation) สำหรับระบบออกแบบ, การจัดการสิทธิ์แบบ least privilege, การใช้ร่องรอยการเข้าถึง (access logs) และ SIEM/SOC สำหรับตรวจจับเหตุผิดปกติ นอกจากนี้ ควรพิจารณาแนวทางเทคนิคเพิ่มเติม เช่น differential privacy, federated learning หรือการใช้ Trusted Execution Environments เพื่อหลีกเลี่ยงการส่ง BOM/ไฟล์ออกจากสภาพแวดล้อมที่ควบคุมได้

การจัดการ model drift และนโยบายการรีเทรน

โมเดล Diffusion-AI ที่ใช้ในการออกแบบ PCB มีความเสี่ยงต่อ model drift เมื่อข้อมูลอินพุต กระบวนการผลิต หรือข้อกำหนดลูกค้าปรับเปลี่ยนตามกาลเวลา หากไม่มีการเฝ้าระวัง โมเดลอาจให้คำแนะนำที่ล้าสมัยหรือไม่สอดคล้องกับเทคโนโลยีการผลิตที่เปลี่ยนไป ซึ่งอาจย้อนกลับมาเป็นงานซ้ำ เพิ่มข้อบกพร่อง หรือก่อให้เกิดปัญหาบนไลน์ผลิต

แนะนำให้ตั้งระบบ MLOps ที่ประกอบด้วยการตรวจวัดเชิงปริมาณ (เช่น การวัดความแม่นยำของการออกแบบ, อัตราการกลับงาน, หรือระยะเวลาแก้ไขต่อกรณี) และตัวชี้วัดการดริฟท์ (เช่น distribution divergence, KL divergence, PSI) โดยกำหนดเกณฑ์ชัดเจนสำหรับการรีเทรน เช่น เมื่อประสิทธิภาพลดลงเกิน 3–5% หรือเมื่อตัวชี้วัดดริฟท์เกินค่าที่กำหนด ควรมีนโยบายรีเทรนแบบผสมผสานระหว่าง scheduled retraining (ทุกไตรมาสหรือทุก 6 เดือน ขึ้นกับอัตราการเปลี่ยนแปลงของผลิตภัณฑ์) และ triggered retraining เมื่อฝั่งการผลิตหรือฟีดแบ็กแจ้งความผิดปกติ

ประเด็นความรับผิดชอบทางกฎหมายและมาตรฐานอุตสาหกรรมที่เกี่ยวข้อง

เมื่อ AI ให้คำแนะนำการออกแบบผิดพลาดจนก่อให้เกิดข้อบกพร่องในผลิตภัณฑ์ จะเกิดคำถามเรื่องความรับผิดชอบ (liability) ทั้งจากมุมสัญญาระหว่างผู้ผลิตและลูกค้า และจากข้อกฎหมายเกี่ยวกับผลิตภัณฑ์และความปลอดภัย การกำหนดขอบเขตความรับผิดชอบต้องชัดเจนในสัญญา: ระบุว่าใครเป็นผู้รับผิดชอบการตรวจสอบขั้นสุดท้าย ใครรับผิดชอบค่าเสียหาย และมีเงื่อนไขการป้องกัน (indemnity, liability cap, SLA) อย่างไร

มาตรฐานที่ควรตรวจสอบและบูรณาการกับกระบวนการ AI ได้แก่:

- IPC: IPC‑A‑600 (Acceptability of Printed Boards), IPC‑2221 (Generic Standard on Printed Board Design), IPC‑6012 (Qualification and Performance for Rigid PCBs) — ใช้เป็นหลักเกณฑ์การยอมรับงานออกแบบและการตรวจสอบ DFM/DFT

- UL: เช่น UL 796 (Standard for Printed-Wiring Boards) และมาตรฐานความปลอดภัยที่เกี่ยวข้องกับไฟฟ้าและไฟลุก เพื่อยืนยันความปลอดภัยของบอร์ดในงานใช้งานจริง

- ISO และมาตรฐานการจัดการ: ISO 9001 (ระบบบริหารคุณภาพ), ISO/IEC 27001 (การจัดการความปลอดภัยสารสนเทศ), และสำหรับอุตสาหกรรมเฉพาะ เช่น ISO 26262 (ยานยนต์) หรือ AS9100 (อากาศยาน) หากลูกค้ามีเงื่อนไขเหล่านี้

แนวทางปฏิบัติที่แนะนำเพื่อบริหารความเสี่ยง

เพื่อผสาน AI เข้ากับกระบวนการออกแบบอย่างปลอดภัยและรับผิดชอบ แนะนำชุดมาตรการดังต่อไปนี้:

- Human-in-the-loop & Sign-off: กำหนดให้วิศวกรรับผิดชอบตรวจสอบและลงนามอนุมัติการออกแบบสุดท้ายก่อนส่งเข้าไลน์ผลิต

- Validation & Testing: สร้างชุดการทดสอบอัตโนมัติ (DFM checks, electrical rule checks, thermal/mechanical simulation) ที่จับคู่กับมาตรฐาน IPC/UL ก่อนการอนุมัติ

- Traceability & Audit Trail: บันทึกเวอร์ชันของโมเดล ข้อมูลฝึกอบรม และเหตุผลที่ระบบแนะนำการเปลี่ยนแปลง เพื่อรองรับการตรวจสอบย้อนหลังและข้อพิสูจน์ในกรณีข้อผิดพลาด

- Contractual IP & Liability Clauses: ระบุความเป็นเจ้าของข้อมูล ผลงานทางปัญญา และขอบเขตความรับผิดชอบกับผู้ให้บริการ AI รวมถึงข้อกำหนดการรักษาความลับและการชดใช้ค่าเสียหาย

- Security by Design: เข้ารหัส BOM/ไฟล์, ใช้ VPC/air‑gap เมื่อจำเป็น, จัดการคีย์/ความลับอย่างเข้มงวด และตรวจสอบ third‑party cloud provider ตามมาตรฐาน ISO/IEC 27001

- Continuous Monitoring & Canary Deployment: นำระบบตรวจจับดริฟท์และทดสอบโมเดลกับชุดข้อมูลจริงในกลุ่มเล็กก่อนขยายการใช้งานเต็มรูปแบบ เพื่อให้สามารถ rollback ได้ทันทีเมื่อตรวจพบปัญหา

- Training & Governance: จัดตั้งคณะกรรมการ AI governance ร่วมระหว่างวิศวกรรม คุณภาพ และฝ่ายกฎหมาย กำหนดนโยบายการรีเทรน การอนุมัติโมเดล และการจัดการความเสี่ยงทางกฎหมาย

สรุปแล้ว การนำ NeuroCAD‑Diffuse มาช่วยลดรอบการออกแบบ 60% และข้อบกพร่อง 25% ได้เป็นประโยชน์เชิงธุรกิจชัดเจน แต่การบริหารความเสี่ยงด้านข้อมูล model drift และความรับผิดชอบทางกฎหมายต้องเป็นไปตามกรอบการจัดการที่เข้มงวด โดยผสมผสานมาตรการด้านความปลอดภัย เทคนิคการตรวจสอบ และข้อกำหนดสัญญา เพื่อให้การใช้งาน AI สอดคล้องกับมาตรฐาน IPC/UL/ISO และคุ้มครองทั้งทรัพย์สินขององค์กรและความปลอดภัยของลูกค้า

บทสรุป

การนำระบบ NeuroCAD‑Diffuse ซึ่งเป็นการประยุกต์ใช้ Diffusion‑AI มาออกแบบ PCB อัตโนมัติในโรงงานชิ้นส่วนอิเล็กทรอนิกส์ของประเทศไทย แสดงให้เห็นผลลัพธ์เชิงปฏิบัติที่ชัดเจน โดยสามารถย่นรอบการออกแบบได้ถึง 60% และลดข้อบกพร่องบนไลน์ผลิตลงราว 25% ซึ่งแปลเป็นการประหยัดต้นทุนการพัฒนาและการผลิต รวมทั้งเพิ่มความสามารถในการแข่งขันของผู้ประกอบการ ตัวอย่างเช่น หากรอบการออกแบบเฉลี่ยเดิมอยู่ที่ 10 วัน การลดลง 60% จะทำให้เหลือเพียงประมาณ 4 วัน ส่งผลให้เวลานำผลิตภัณฑ์สู่ตลาด (time‑to‑market) สั้นลงอย่างมีนัยสำคัญและลดต้นทุนค่าแรงและค่าเสียโอกาสจากข้อผิดพลาดบนไลน์ผลิตได้โดยตรง

อย่างไรก็ตาม ผลประโยชน์จาก AI จะเกิดอย่างยั่งยืนก็ต่อเมื่อการนำไปใช้มาพร้อมกับกระบวนการตรวจสอบที่เข้มงวด การบริหารจัดการข้อมูล (data governance) ที่ชัดเจน และแผนการทดสอบเชิงปฏิบัติการ (operational testing) ที่มีการวัดผลเป็นระบบ ต้องมีการกำกับดูแลข้อมูลฝึกสอน การจัดเก็บเวอร์ชันของโมเดล การตั้งค่า human‑in‑the‑loop เพื่อให้มนุษย์ตรวจสอบและอนุมัติการออกแบบในจุดสำคัญ รวมถึงการตั้งเกณฑ์การตรวจจับความเบี่ยงเบนและการเฝ้าติดตามคุณภาพหลังใช้งาน เพื่อป้องกันความเสี่ยงด้านความปลอดภัย การปฏิบัติตามมาตรฐาน และปัญหาทางไซเบอร์ที่อาจเกิดขึ้น

มองไปข้างหน้า NeuroCAD‑Diffuse มีศักยภาพขยายผลได้ทั้งในห่วงโซ่อุปทานอิเล็กทรอนิกส์ การบูรณาการกับระบบ PLM/ECAD และการนำข้อมูลการผลิตจริงกลับมาใช้ปรับปรุงโมเดลแบบปิดวงจร (closed‑loop learning) แต่ความสำเร็จในวงกว้างจำเป็นต้องอาศัยนโยบายการบริหารข้อมูลมาตรฐาน การอบรมบุคลากร และแผนงานด้านการทดสอบและกำกับดูแลเพื่อให้ผลลัพธ์มีความปลอดภัย น่าเชื่อถือ และให้ผลประโยชน์ทางเศรษฐกิจในระยะยาว