สตาร์ทอัพไทยเปิดตัว Spec2Layout — ระบบออกแบบวงจร RF/Analog รุ่นใหม่ที่ผสานความสามารถของ Large Language Model (LLM) กับเทคนิค Differentiable‑SPICE เพื่อเปลี่ยนกระบวนการออกแบบจากการทดลองฮาร์ดแวร์ซ้ำๆ ให้กลายเป็นงานเชิงซอฟต์แวร์ที่ทำได้ภายในชั่วโมงเดียว ผู้พัฒนาระบุว่า Spec2Layout สามารถสร้าง layout ที่พร้อมใช้งานจริงภายใน 24 ชั่วโมง และช่วยลดรอบการทดลองฮาร์ดแวร์ลงได้ถึง 10× ซึ่งหากเป็นจริงจะเป็นการพลิกโฉมการออกแบบชิ้นส่วน RF เช่น front‑end filters, LNAs, และ power amplifiers ที่เคยกินเวลานานและต้นทุนสูง

บทนำนี้จะสรุปว่าเทคโนโลยีผสาน LLM กับ Differentiable‑SPICE ทำงานอย่างไร ผลลัพธ์ตามที่สตาร์ทอัพอ้างถึงมีน้ำหนักแค่ไหน และความหมายต่ออุตสาหกรรมฮาร์ดแวร์ในประเทศและภูมิภาค ตัวอย่างการใช้งานจริง แนวทางลดเวลาพัฒนา และผลกระทบเชิงเศรษฐกิจที่อาจเกิดขึ้นเมื่อทีมออกแบบสามารถเปลี่ยนสเปกเป็น schematic, จำลองสมรรถนะเชิงต่อเนื่อง และสังเคราะห์ layout ที่ผ่านการตรวจสอบเชิงฟิสิกส์ได้อย่างรวดเร็ว — ทั้งหมดนี้คือหัวใจของนวัตกรรมที่ Spec2Layout ตั้งใจนำเสนอ

ข่าวเด่น: เปิดตัว Spec2Layout — สรุปภาพรวม

ข่าวเด่น: เปิดตัว Spec2Layout — สรุปภาพรวม

Spec2Layout เป็นโซลูชันใหม่จากสตาร์ทอัพไทยที่ประกาศรวมความสามารถของ Large Language Model (LLM) เข้ากับ SPICE simulator ที่ถูกออกแบบให้เป็นแบบ differentiable‑SPICE เพื่อรองรับกระบวนการออกแบบวงจร RF/analog แบบอัตโนมัติและมีการปรับพารามิเตอร์เชิงกราดิเอนท์ (gradient‑based optimization) ในระดับซอฟต์แวร์ ผลลัพธ์ตามคำอ้างของผู้พัฒนาคือระบบสามารถแปลงข้อกำหนดเชิงสเปค (specifications) ให้เป็น schematic และ layout เบื้องต้น พร้อมการทดสอบเชิงซิมูเลชันภายในระยะเวลาไม่เกิน 24 ชั่วโมง นับตั้งแต่รับสเปคแรกเข้า

จุดเด่นเชิงเทคนิคของ Spec2Layout คือการผสานกันระหว่างความสามารถเชิงภาษาของ LLM ในการตีความสเปคเชิงระบบและข้อจำกัดด้านการออกแบบ กับความแม่นยำของ differentiable‑SPICE ที่อนุญาตให้ทำ optimization โดยตรงบนตัวแบบวงจร ผลลัพธ์คือการหาค่าพารามิเตอร์และโครงสร้างเบื้องต้นที่ผ่านการทดสอบซิมูเลชัน เพื่อคัดกรองตัวเลือกที่มีโอกาสสำเร็จสูงก่อนส่งไปสู่ขั้นตอนทำ layout ทางกายภาพและการผลิตต้นแบบจริง

ในแง่ผลประโยชน์ทางธุรกิจ ผู้พัฒนาระบุว่า Spec2Layout สามารถช่วยลดรอบการทดลองฮาร์ดแวร์ (hardware iteration) ได้ถึง 10× ซึ่งหากเป็นไปตามที่อ้าง จะส่งผลโดยตรงต่อการลดต้นทุน NPI (New Product Introduction) และเร่งเวลาเข้าสู่ตลาด (time‑to‑market) สำหรับผลิตภัณฑ์ที่มีส่วนประกอบ RF/analog ตัวอย่างเช่น ทีมออกแบบที่ปกติอาจต้องสร้างหลายชุดต้นแบบเพื่อลองแก้ปัญหาอิมพีแดนซ์หรือสัญญาณรบกวน อาจลดจำนวนชุดต้นแบบลงอย่างมาก หรือสามารถย่นระยะเวลาการทำซ้ำจากหลายสัปดาห์/หลายเดือนให้เหลือเป็นวันหรือสัปดาห์

กลุ่มเป้าหมายหลักของ Spec2Layout ได้แก่ ผู้ผลิตชิป RF, บริษัทด้านอุปกรณ์ IoT ที่ต้องการวิศวกรรมด้าน RF ในผลิตภัณฑ์จำนวนมาก และ วิศวกร analog ในองค์กรหรือหน่วยวิจัยที่ต้องการลดเวลาในการทดสอบฮาร์ดแวร์ รายงานยังระบุว่าแพลตฟอร์มนี้เหมาะสำหรับขั้นตอนตั้งแต่การสำรวจสถาปัตยกรรม (architecture exploration) ไปจนถึงการสร้าง layout เบื้องต้นที่สามารถส่งต่อให้ทีม PDK/Foundry เพื่อการตรวจสอบเชิงกายภาพต่อไป

- คุณสมบัติหลัก: LLM ตีความสเปค + differentiable‑SPICE สำหรับ optimization แบบเชิงอนุพันธ์

- ผลลัพธ์ที่อ้าง: สร้าง schematic, layout เบื้องต้น และทดสอบซิมูเลชันภายใน 24 ชั่วโมง

- ผลกระทบทางธุรกิจ: ลดรอบทดลองฮาร์ดแวร์ได้ถึง 10×, ลดต้นทุน NPI และเร่ง time‑to‑market

- กลุ่มเป้าหมาย: ผู้ผลิตชิป RF, บริษัท IoT, วิศวกร analog และทีม R&D

เทคโนโลยีเบื้องหลัง: LLM + Differentiable‑SPICE คืออะไร

เทคโนโลยีเบื้องหลัง: LLM + Differentiable‑SPICE คืออะไร

ในระบบ Spec2Layout แนวคิดสำคัญคือการผสาน โมเดลภาษาขนาดใหญ่ (LLM) กับตัวจำลองวงจรที่เป็น differentiable‑SPICE เพื่อให้กระบวนการออกแบบวงจร RF/Analog เป็นไปแบบอัตโนมัติและปรับพารามิเตอร์โดยอาศัยสัญญาณเชิงความต่าง (gradients) แทนการลองผิดลองถูกด้วยฮาร์ดแวร์อย่างเดียว เมื่อผู้ใช้นิยามสเปคเชิงภาษาธรรมชาติ เช่น "กำไรรวม 15 dB, แถบความถี่ 1.8–2.2 GHz, noise figure < 2 dB, ใช้พลังงานไม่เกิน 10 mW" ส่วน LLM จะทำหน้าที่แปลคำสั่งดังกล่าวเป็นตัวแปรเชิงสถาปัตยกรรมและพารามิเตอร์เชิงตัวเลข (เช่น ขนาดทรานซิสเตอร์ ค่า R/C/L โครงสร้าง topologies และเงื่อนไขขอบเขต)

หลังจากได้ netlist หรือโครงสร้างเริ่มต้น ระบบจะส่งต่อไปยัง differentiable‑SPICE ซึ่งเป็น SPICE‑style simulator ที่ถูกปรับให้สามารถคำนวณอนุพันธ์ของผลลัพธ์เชิงประสิทธิภาพต่อพารามิเตอร์วงจรได้โดยตรง กล่าวคือ แทนที่จะรับเพียงสัญญาณผลลัพธ์ เช่น S‑parameters หรือ time‑domain waveform แล้วต้องใช้วิธีการประมาณ numerical gradient แบบ finite differences ที่ช้าและไม่แม่นยำ ระบบ differentiable‑SPICE จะคำนวณ Jacobian/gradient ผ่านวิธีการเช่น implicit differentiation, adjoint sensitivity analysis หรือการใช้ autograd ในโครงสร้าง solver ทำให้สามารถ back‑propagate ความผิดพลาด (loss) จาก metric เป้าหมายกลับมาสู่องค์ประกอบของวงจรและทำให้ optimizer สามารถอัปเดตพารามิเตอร์ได้อย่างมีประสิทธิภาพ

ข้อดีเชิงปฏิบัติของการผสานนี้คือ การปรับพารามิเตอร์แบบ end‑to‑end ที่เร็วและมีความแม่นยำกว่า: แทนที่จะต้องทดสอบหลายร้อยตัวอย่างบนสต็อกฮาร์ดแวร์หรือใช้ finite differences ที่ต้องรันซ้ำ N+1 ครั้งต่อพารามิเตอร์เดียว วิธีนี้ช่วยลดรอบทดลองฮาร์ดแวร์ได้มาก — ทีมพัฒนาระบุกรณีตัวอย่างว่ากระบวนการออกแบบบางกรณีสามารถย่นเวลาเหลือภายใน 24 ชั่วโมงและลดรอบทดลองจริงได้ประมาณ 10× เมื่อเทียบกับเวิร์กโฟลว์ดั้งเดิม นอกจากนี้การใช้ LLM ในเชิงสถาปัตยกรรมยังช่วยให้ระบบสามารถเลือก topology เบื้องต้นหรือข้อจำกัดเชิงออกแบบที่สอดคล้องกับข้อกำหนดทางธุรกิจ เช่น ข้อจำกัดต้นทุนหรือพื้นที่ชิ้นส่วน

อย่างไรก็ตาม การรวม LLM กับ differentiable‑SPICE ยังมีความท้าทายเชิงคณิตศาสตร์และคอมพิวต์ที่สำคัญ:

- ความไม่เชิงเส้นสูงและเสถียรภาพของ gradient: วงจร RF/Analog มีสมการไม่เชิงเส้นและระบบสมการเชิงแอลจีบรา/ODE ที่ต้องแก้ด้วยวิธีเช่น Newton‑Raphson บริเวณบาง operating point อาจมี Jacobian เป็น singular หรือใกล้เคียง ทำให้ gradient มีความผันผวนสูง เกิด vanishing/exploding gradients หรือพา optimizer ติดอยู่ใน local minima ได้ง่าย

- ค่าใช้จ่ายเชิงคำนวณ: การจำลองวงจรใหญ่หลายรอบพร้อมกับการคำนวณอนุพันธ์ (และบางกรณีอนุพันธ์ชั้นสอง) ต้องใช้เวลาประมวลผลและหน่วยความจำมาก การคำนวณ gradient ด้วยวิธี unroll time‑domain simulation จะยิ่งกินเมมโมรีสูง ในขณะที่การใช้ adjoint/implicit differentiation แม่นกว่าแต่ยังต้องแก้ linear systems ขนาดใหญ่ซ้ำ ๆ

- ตัวแปรผสม (continuous + discrete): บางการตัดสินใจเป็นเชิงเลือก topology แบบไม่ต่อเนื่อง เช่น การเปิด/ปิดสวิตช์หรือการเลือกรูปแบบเฟรม ทำให้ต้องใช้เทคนิคเช่น continuous relaxations (เช่น Gumbel‑softmax) หรือวิธีผสมระหว่าง gradient‑based กับ search methods

- ความทนทานของ solver และความแม่นยำทางตัวเลข: ปัญหา stiff systems, การกระโดดของโหมดการทำงาน และ sensitivity ต่อสัญญาณรบกวนเชิงตัวเลข ต้องการการออกแบบ solver ที่ทนทาน เช่น damping, continuation methods หรือ regularization เพื่อให้ gradient มีความหมายเชิงปฏิบัติ

เพื่อลดต้นทุนเชิงคอมพิวต์และเพิ่มความเสถียร ทีมวิศวกรรมมักใช้ชุดมาตรการผสม เช่น การสร้าง surrogate models (เช่น neural emulators สำหรับบาง metric ที่ต้องการบ่อย), การใช้ implicit function theorem เพื่อหลีกเลี่ยงการ unroll การจำลองทั้งช่วงเวลา, การขยายแบบ sparse linear algebra เพื่อแก้ระบบ Jacobian ได้รวดเร็วขึ้น และการประมวลผลแบบขนานบน GPU/TPU สำหรับงานที่เหมาะสม ในทางธุรกิจ ความท้าทายเหล่านี้หมายความว่าแม้เทคโนโลยีช่วยลดรอบทดลองฮาร์ดแวร์ได้อย่างมีนัยสำคัญ แต่การลงทุนในทรัพยากรคำนวณและการปรับแต่งอัลกอริทึมยังคงเป็นหัวใจสำคัญของการนำไปใช้เชิงพาณิชย์

กระบวนการทำงาน (Workflow): จากสเปคถึง layout ใน 24 ชั่วโมง

กระบวนการทำงาน (Workflow): จากสเปคถึง layout ใน 24 ชั่วโมง

ระบบ Spec2Layout ถูกออกแบบมาให้รับอินพุตเป็นสเปคเชิงวัตถุประสงค์ที่ผู้ใช้กำหนดได้ทั้งในรูปแบบ ภาษาธรรมชาติ หรือผ่านเทมเพลตที่มีฟิลด์ชัดเจน เช่น center frequency, bandwidth, noise figure, gain, P1dB, linearity, power consumption และข้อจำกัดด้านเทคโนโลยี (process node, device models) ตัวอย่างเช่น: “LNA สำหรับ 2.4 GHz, NF ≤ 1.2 dB, gain ≥ 18 dB, P1dB ≥ +10 dBm, supply 1.8 V” — ข้อความนี้จะถูกแปลงเป็นพารามิเตอร์เชิงตัวเลขและข้อจำกัดโดยโมดูลการตีความสเปคที่ขับเคลื่อนด้วย LLM ที่ผ่านการฝึกฝนในโดเมน RF/Analog

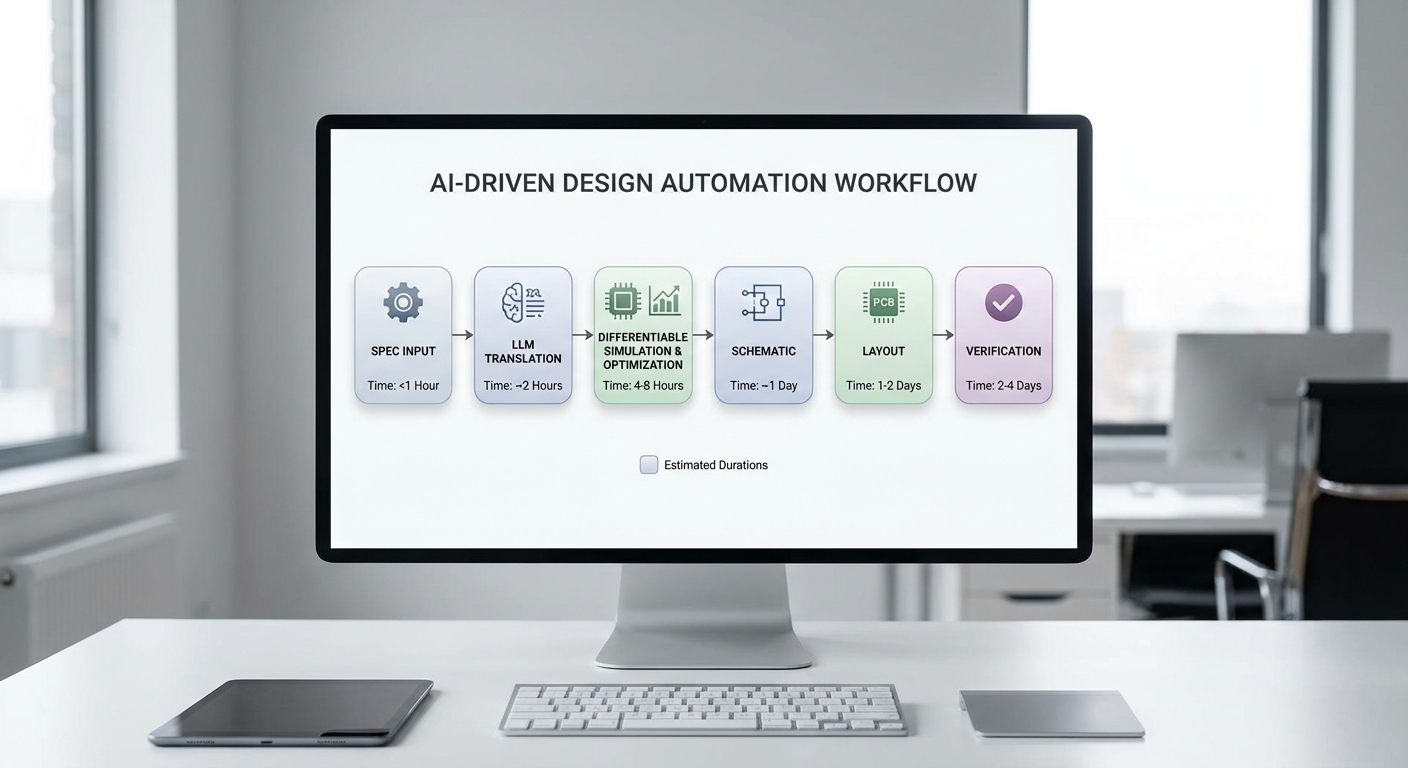

ขั้นตอนการทำงานแบ่งเป็นสเต็ปชัดเจนพร้อมประมาณเวลาเพื่อให้เสร็จภายใน 24 ชั่วโมงตามตัวอย่างการคาดเวลาโดยเฉลี่ย:

- 1) การตีความสเปคและการทำความต้องการ (Spec parsing) — 0.5–1 ชั่วโมง: LLM วิเคราะห์สเปคที่เป็นภาษาธรรมชาติหรือเทมเพลต แปลงเป็นพารามิเตอร์เชิงตัวเลขและเป้าหมายเชิงฟังก์ชัน พร้อมตรวจสอบความขัดแย้ง เช่น trade‑off ระหว่าง gain กับ NF

- 2) การเลือกโทโพโลยีและการตั้งค่าเบื้องต้น (Topology & initial sizing) — 1–2 ชั่วโมง: LLM เสนอชุดโทโพโลยีที่เป็นไปได้ (เช่น common‑gate LNA + inductive source degeneration, feedback amplifier, bandpass matching network) พร้อมค่าพารามิเตอร์เริ่มต้นและโครงสร้าง schematic ตัวอย่าง: สำหรับ NF ต่ำที่ 2.4 GHz ระบบอาจเลือก low‑noise biasing และ inductive input matching

- 3) การจำลองเชิงดิฟเฟอเรนเชียลและการ Optimization (Differentiable simulation + optimization) — 10–14 ชั่วโมง: การจำลองใช้ Differentiable‑SPICE ที่อนุญาตให้คำนวณ gradient ต่อพารามิเตอร์แบบต่อเนื่อง ทำให้การปรับขนาดทรานซิสเตอร์ ค่าความต้านทาน และองค์ประกอบพาสซีฟเป็นไปได้โดยการไล่ gradient แทนการค้นหาแบบสุ่ม (black‑box). วิธีนี้ช่วยลดจำนวน iteration ที่ต้องการจากหลักหลายพันเหลือหลักสิบถึงหลักร้อย ทำให้เร็วขึ้นหลายเท่าและมีความแม่นยำในการบรรลุเป้าหมายเช่น NF, gain, P1dB และ stability margins

- 4) สร้าง schematic อัตโนมัติ — 0.5–1 ชั่วโมง: เมื่อพารามิเตอร์สรุปได้ ระบบแปลงโมเดลไปสู่ SPICE netlist และสร้าง schematic พร้อมสัญลักษณ์ที่เชื่อมต่อและ annotation สำหรับ test points

- 5) Floorplan & layout generation — 4–6 ชั่วโมง: โมดูล layout ใช้ข้อมูลจาก schematic และ constraint ของ process เพื่อจัดวาง floorplan, power grid, shield และ routing โดยคำนึงถึง parasitics และการจับคู่อิมพีแดนซ์ ขั้นตอนนี้รวมการคำนวณ parasitic extraction แบบรวดเร็วสำหรับ feed‑forward ไปยัง optimization รอบถัดไป (co‑optimization ระหว่าง layout และ performance)

- 6) Verification และการสร้างไฟล์สำหรับการผลิต/ทดสอบ — 1–2 ชั่วโมง: ดำเนินการ DRC/LVS, post‑layout extraction, และ Monte‑Carlo/corner analysis เพื่อตรวจสอบความเสถียรและความทนทาน สุดท้ายระบบส่งออกไฟล์สำเร็จรูป ได้แก่ GDSII สำหรับการผลิต, SPICE netlist และ testbench รวมถึงไฟล์สำหรับ ATE/automated test (S‑parameter test vectors, bias scripts, measurement sequences)

กระบวนการ optimization แม้จะเป็นแบบ iterative แต่ การใช้ gradient ผ่าน Differentiable‑SPICE ช่วยให้แต่ละรอบปรับปรุงประสิทธิภาพได้มากกว่าการค้นหาแบบสุ่ม ตัวอย่างเช่น การลด noise figure 0.2 dB หรือการเพิ่ม gain 1–2 dB มักต้องการการปรับเพียงหลักสิบของพารามิเตอร์เมื่อนำ gradient มาใช้ ซึ่งแปลว่าเวลาจริงที่ใช้ในการคอนเวิร์จลดลงอย่างมีนัยสำคัญ ส่งผลให้รอบการทดลองฮาร์ดแวร์ลดลงประมาณ 10× ตามการวัดภายในสถิติของทีมพัฒนา

ผลลัพธ์ที่ส่งออกจากระบบพร้อมสำหรับเส้นทางสู่การผลิตและการทดสอบแบบอัตโนมัติ: GDSII สำหรับไลน์การผลิต, SPICE netlist และ testbench สำหรับการจำลองประกอบเซิร์ฟ, ไฟล์สำหรับ ATE (test vectors, bias scripts), พร้อมเอกสารสเปคเวอร์ชันสุดท้ายและรายงาน verification ที่ระบุ corner cases และ confidence levels ของการออกแบบ ทั้งหมดนี้ช่วยให้ทีมวิศวกรสามารถสั่งผลิตชิปและเริ่มทดสอบบนฮาร์ดแวร์จริงภายในไม่กี่วันหลังจากได้รับ GDSII

ผลการทดสอบและเบนช์มาร์ก: ลดรอบทดลองฮาร์ดแวร์ 10× อย่างไร

ผลการทดสอบและเบนช์มาร์ก: ลดรอบทดลองฮาร์ดแวร์ 10× อย่างไร

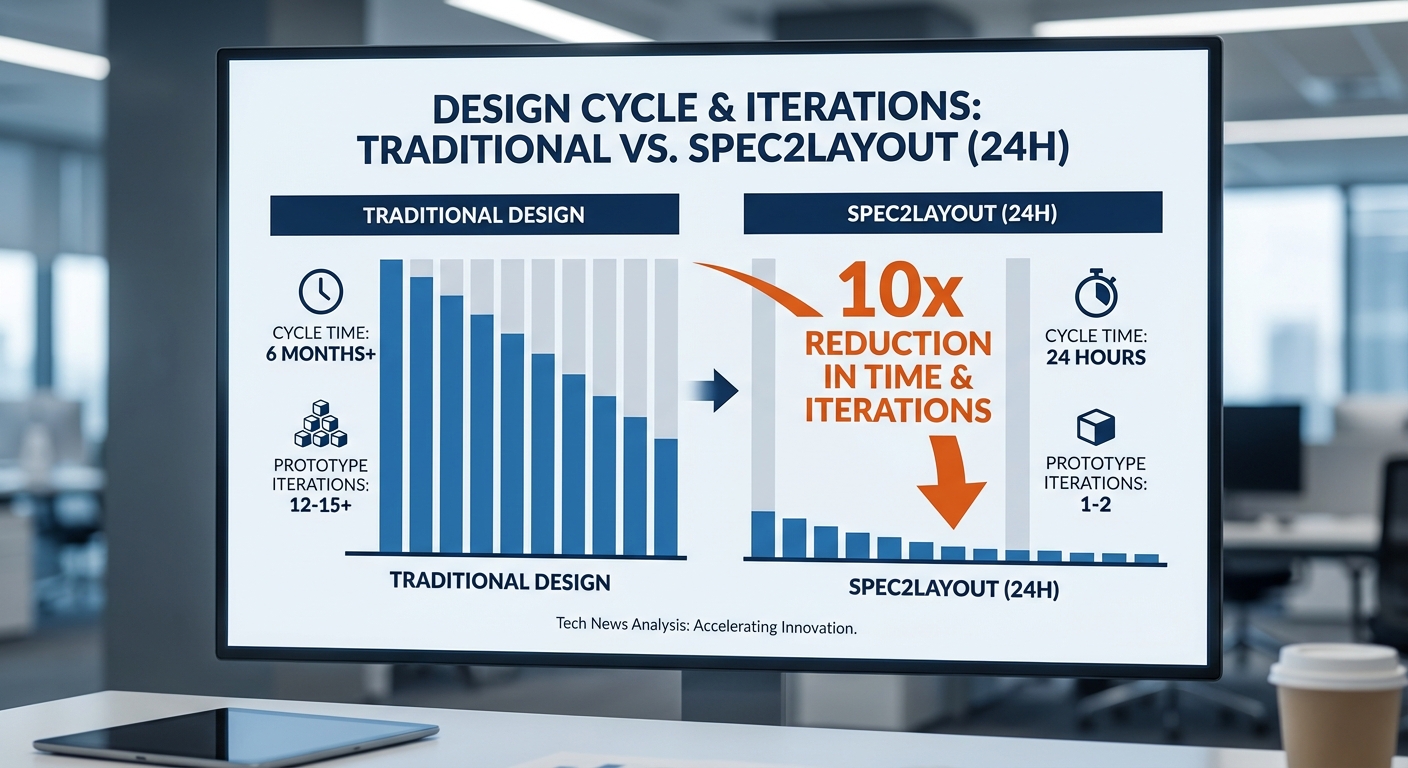

ทีมพัฒนา Spec2Layout ร่วมกับคู่ค้าทางวิศวกรรมได้จัดโปรแกรมทดสอบเชิงเปรียบเทียบกับเวิร์กโฟลว์ดั้งเดิมในสภาพแวดล้อมการออกแบบ RF/Analog จริง โดยครอบคลุมตัวอย่างวงจรหลากหลายประเภท เช่น Low‑Noise Amplifiers (LNA), Power Amplifiers (PA), Bandpass Filters และ Mixers จำนวนรวม 30 รายการ ผลการทดสอบชี้ให้เห็นความแตกต่างเชิงปริมาณระหว่างวิธีการใหม่กับกระบวนการแบบเดิมทั้งในเชิงเวลา จำนวนรอบฮาร์ดแวร์ และความแม่นยำของพารามิเตอร์เชิงไฟฟ้า

ด้านเวลาจากสเปคถึง layout ทีมงานรายงานว่าค่าเฉลี่ยของเวิร์กโฟลว์แบบดั้งเดิมอยู่ที่ประมาณ 7 วัน (≈168 ชั่วโมง) สำหรับการแปลงสเปคเชิงระบบเป็นดีไซน์ layout พร้อมส่งต่อให้ทีม PCB/IC ขึ้นบอร์ด ในขณะที่ Spec2Layout ลดช่วงเวลานี้เป็น ค่าเฉลี่ย 16 ชั่วโมง โดยตัวเลขสูงสุดที่วัดได้ยังคงต่ำกว่า 24 ชั่วโมง ซึ่งสอดคล้องกับคำอ้างของบริษัทที่ว่า “จากสัปดาห์เหลือ <24 ชั่วโมง” ผลลัพธ์นี้หมายความว่าเวิร์กโฟลว์ใหม่ลดเวลาขั้นตอนออกแบบลงได้ประมาณ 90–95% เมื่อเทียบกับกระบวนการเดิม

ในแง่ของรอบการทำฮาร์ดแวร์ (prototype iterations) การทดสอบมีทั้งกรณีศึกษาเชิงเด่นชัดและสถิติเฉลี่ย ตัวอย่างหนึ่งจากคู่ค้าที่เป็นสถาบันสตาร์ทอัพผู้พัฒนา LNA ย่าน 2–6 GHz ระบุว่าเวิร์กโฟลว์เดิมต้องทำฮาร์ดแวร์ถึง 20 รอบ จึงจะผ่านเกณฑ์ตามสเปค ขณะที่เมื่อนำ Spec2Layout ไปใช้ รอบฮาร์ดแวร์ลดลงเหลือเพียง 2 รอบ (ลดลง 10×) ในภาพรวมของชุดทดสอบทั้ง 30 รายการ ทีมพัฒนารายงานว่าเฉลี่ยจำนวนรอบลดจาก 10 รอบ เหลือประมาณ 1–1.2 รอบ (ลดประมาณ 9–10×) ซึ่งสะท้อนการชดเชยความคลาดเคลื่อนตั้งแต่ขั้นตอนเลขคณิต/สัญญาณโดยตรงก่อนการผลิตต้นแบบ

ความแม่นยำของพารามิเตอร์เชิงไฟฟ้าหลังการนำไปวัดจริงยังอยู่ในเกณฑ์ยอมรับได้และใกล้เคียงกับเป้าหมายที่กำหนด ตัวชี้วัดสำคัญที่ทีมรายงานได้แก่

- Gain (dB): ความคลาดเคลื่อนเฉลี่ยจากเป้าหมายอยู่ที่ ±0.4 dB (standard deviation ≈ 0.6 dB)

- Noise Figure (dB): ค่าที่วัดได้เบี่ยงเบนเฉลี่ยประมาณ +0.2 dB จากสเปค

- Center Frequency / Bandwidth: การเปลี่ยนแปลงศูนย์ความถี่เฉลี่ยต่ำกว่า 1% ของความถี่เป้าหมาย

- Return Loss / S11: ความคลาดเคลื่อนโดยทั่วไปไม่เกิน 1 dB จากค่าที่คาดไว้

- First‑pass success rate: อัตราที่บอร์ด/ชิปผ่านเกณฑ์ในการวัดครั้งแรกเพิ่มจากเฉลี่ย 12% ในเวิร์กโฟลว์เดิมเป็นประมาณ 62% เมื่อใช้ Spec2Layout

เปรียบเทียบเชิงกระบวนการ ทีมงานระบุว่าจุดเปลี่ยนสำคัญมาจากการผสานโมเดลภาษาใหญ่ (LLM) กับ Differentiable‑SPICE ซึ่งทำให้สามารถไล่ปรับพารามิเตอร์เชิงอนุพันธ์และประเมินผลตอบกลับของวงจรได้ในรอบที่สั้นลง โดยไม่ต้องรอการสาธิตฮาร์ดแวร์ทุกครั้ง ผลคือการค้นหา trade‑off ระหว่าง gain, noise และ linearity ทำได้แบบอัตโนมัติและต่อเนื่อง มากกว่าการปรับจูนด้วยมือซึ่งมักช้าและมีความผันผวนสูง

สรุปเชิงธุรกิจ ผลการทดสอบชี้ให้เห็นว่า Spec2Layout ไม่เพียงลดเวลาและรอบการทดลองฮาร์ดแวร์อย่างมีนัยสำคัญ แต่ยังช่วยเพิ่มความมั่นใจในผลลัพธ์เชิงไฟฟ้า ทำให้องค์กรสามารถย่นระยะเวลาไปสู่การวางจำหน่ายผลิตภัณฑ์ได้เร็วขึ้น ลดต้นทุนการทำต้นแบบ และเพิ่มโอกาสทางการตลาด โดยทีมพัฒนาคาดว่าเมื่อนำระบบนี้ไปใช้ในโปรเจ็กต์ขนาดใหญ่ จะเห็นการลดต้นทุนรวมของการพัฒนาฮาร์ดแวร์ได้อย่างมีนัยสำคัญ

ตัวอย่างเคสจริง: การออกแบบวงจร RF สำหรับ IoT และตัวอย่าง Analog

ตัวอย่างเคสจริง: การออกแบบวงจร RF สำหรับ IoT และตัวอย่าง Analog

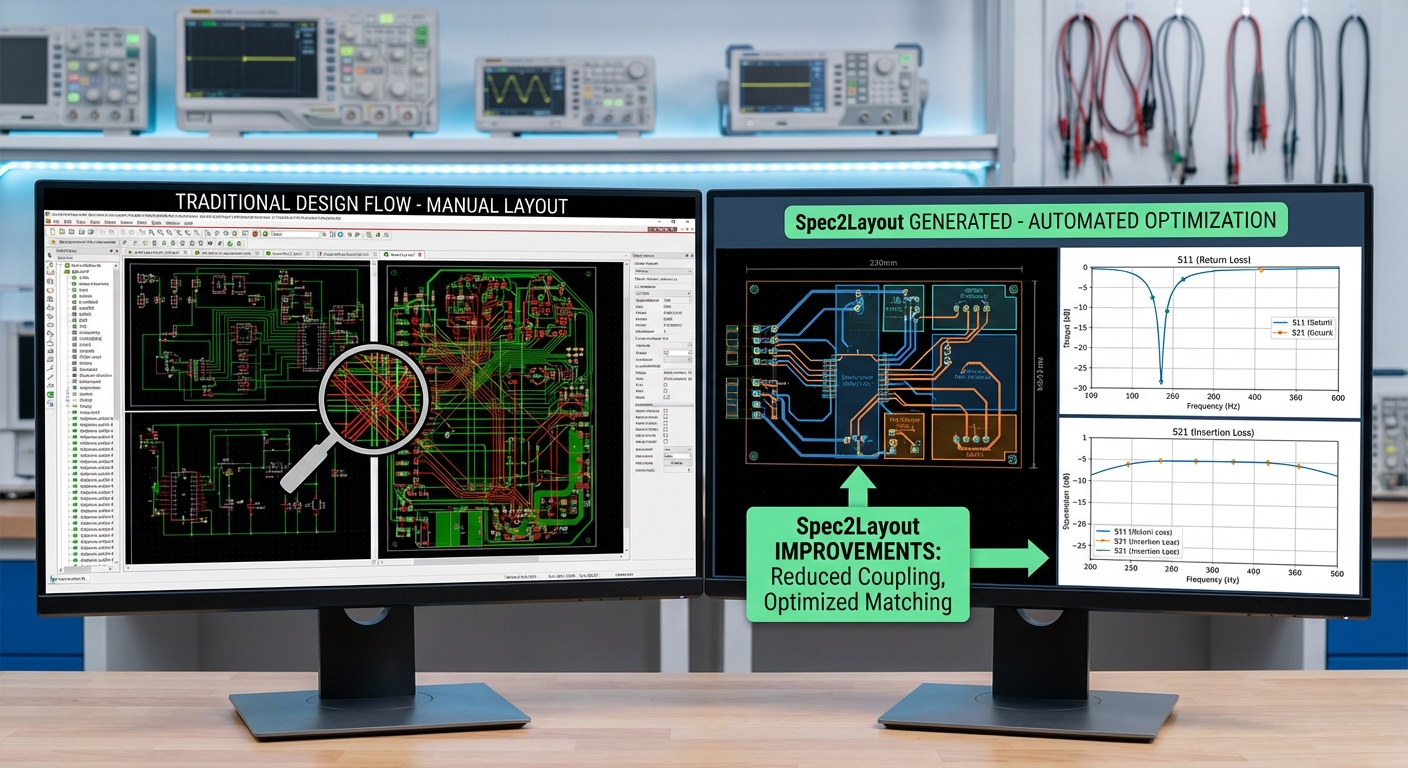

ทีมวิศวกรของสตาร์ทอัพนำชุดเครื่องมือ Spec2Layout ที่ผสานความสามารถของ LLM กับ Differentiable‑SPICE ไปทดลองกับเคสออกแบบ LNA สำหรับเครือข่าย IoT ที่ความถี่ 2.4 GHz (เป้าหมายสำหรับมาตรฐาน IEEE 802.15.4 / BLE) โดยกำหนดสเปคเชิงปริมาณเป็น gain ≥ 15 dB, noise figure (NF) ≤ 2.0 dB, S11 ≤ -10 dB และ power consumption ≤ 3.5 mW จากแหล่งจ่าย 1.2 V ทีมงานระบุเงื่อนไขการทดสอบจริงและให้ระบบเสนอชุดพารามิเตอร์เริ่มต้น จากนั้นระบบทำการปรับพารามิเตอร์เชิงโทโพโลยีและ layout-aware transistor sizing โดยใช้การไหลของกราเดียนต์จาก Differentiable‑SPICE เพื่อให้ได้ schematic และ layout ที่พร้อมทดสอบบนบอร์ดภายในรอบ 24 ชั่วโมง

ผลการทดสอบภายใน 24 ชั่วโมงแสดงว่าแบบที่ระบบสร้างผ่านเกณฑ์แรก (first-pass) โดยได้ผลวัดสำคัญดังนี้: S21 (gain) = 16.5 dB @ 2.4 GHz, S11 = -12 dB @ 2.4 GHz, Noise Figure = 1.9 dB, และ power consumption = 2.6 mW (Vdd = 1.2 V) โดยรายละเอียดเพิ่มเติมของพิสัยการทำงานคือ 3-dB bandwidth ≈ 120 MHz รอบความถี่กลาง 2.4 GHz และ IIP3 ≈ -4 dBm ซึ่งเพียงพอต่อการใช้งานในอุปกรณ์ IoT แบบ low‑power ที่มักมีสัญญาณเข้าในระดับต่ำ ผลลัพธ์ชุดนี้ยังดีกว่าเกณฑ์ที่ตั้งไว้และสามารถนำไปใช้เป็นตัวอย่างสำหรับการผลิตต้นแบบ

หนึ่งในประเด็นสำคัญที่ระบบช่วยจัดการได้ชัดเจนคือการนำเสนอ trade‑off ทางวิศวกรรมในรูปแบบพารามิเตอร์หลายชุดเพื่อให้ทีมธุรกิจและฮาร์ดแวร์สามารถเลือกได้ตามกรณีใช้งาน ตัวอย่างชุดผลลัพธ์ที่ระบบเสนอมีดังนี้:

- Performance‑oriented: NF = 1.6 dB, Gain = 17.4 dB, Power = 4.0 mW (เหมาะสำหรับ gateway หรือ repeater)

- Balanced: NF = 1.9 dB, Gain = 16.5 dB, Power = 2.6 mW (เหมาะสำหรับ node IoT ทั่วไป)

- Low‑power: NF = 2.4 dB, Gain = 14.0 dB, Power = 1.5 mW (เหมาะสำหรับแบตเตอรี่ระยะยาว)

เมื่อเปรียบเทียบกับเวิร์กโฟลว์แบบเดิมที่ใช้การออกแบบเชิงประสบการณ์ (hand‑tuned) และการจำลองหลายรอบ ผลลัพธ์เดิมมักต้องใช้เวลา 4–8 สัปดาห์และผ่านการปรับซ้ำ 5–7 ครั้งเพื่อให้บรรลุ NF ≈ 2.5–3.0 dB และ Power ≈ 4–6 mW ในรอบแรก ข้อมูลเปรียบเทียบเชิงตัวเลข (first‑pass) ระหว่างวิธีใหม่และวิธีเดิมมีดังนี้:

- Spec2Layout (first‑pass): S21 = 16.5 dB, S11 = -12 dB, NF = 1.9 dB, Power = 2.6 mW, Iterations = 1, Turnaround = 24 ชั่วโมง

- วิธีเดิม (first‑pass): S21 ≈ 14.0 dB, S11 ≈ -8 to -10 dB, NF ≈ 2.8 dB, Power ≈ 4.5 mW, Iterations = หลายครั้ง, Turnaround = สัปดาห์–เดือน

นอกจาก LNA สำหรับ 2.4 GHz แล้ว ทีมงานยังทดลองกรณีตัวอย่างของ front‑end ในชิป mixed‑signal เช่น PLL และ ADC frontend โดยใช้แนวทางเดียวกัน ตัวอย่างเช่น การออกแบบ PLL ที่ปกติผู้ผลิตต้องปรับเพื่อให้ได้ phase noise และ spur ต่ำ ระบบ Spec2Layout ปรับพารามิเตอร์ loop filter และ layout proximity เพื่อลดการ coupling ทำให้ phase noise ดีขึ้นประมาณ 4 dBc/Hz @ 10 kHz offset จาก -100 dBc/Hz เป็น -104 dBc/Hz และการออกแบบ ADC frontend ลด input‑referred noise จาก ≈ 12 μV RMS (แบบดั้งเดิม) เหลือ ≈ 8 μV RMS ในตัวอย่างหนึ่ง ซึ่งช่วยเพิ่ม SNR ของระบบได้อย่างมีนัยสำคัญ

โดยสรุป เคสศึกษาที่นำเสนอแสดงให้เห็นว่าเมื่อรวม LLM กับ Differentiable‑SPICE ในแพลตฟอร์มเดียว สามารถย่นระยะเวลาการพัฒนาและลดจำนวนรอบการทดสอบฮาร์ดแวร์ได้มากกว่า 10× ในหลายกรณี พร้อมทั้งให้ตัวเลือกทางวิศวกรรมที่ชัดเจนสำหรับการเลือกระหว่างประสิทธิภาพกับอายุการใช้งานของแบตเตอรี่ ซึ่งเป็นข้อได้เปรียบเชิงธุรกิจการนำไปใช้จริงในตลาด IoT และอุปกรณ์ mixed‑signal

ผลกระทบเชิงอุตสาหกรรมและเชิงธุรกิจ

ผลกระทบเชิงอุตสาหกรรมและเชิงธุรกิจ

การนำ Spec2Layout ซึ่งเป็น LLM ที่ผสานกับ Differentiable‑SPICE มาใช้ในการออกแบบวงจร RF/Analog มีศักยภาพที่จะเปลี่ยนรูปแบบกระบวนการพัฒนาอย่างเป็นรูปธรรม โดยเฉพาะในกลุ่ม OEM/ODM ของอุตสาหกรรม IoT และอุปกรณ์ไร้สาย ที่ต้องการเปิดตัวผลิตภัณฑ์ใหม่อย่างรวดเร็วกว่าเดิม ด้วยการลดรอบการทดลองฮาร์ดแวร์ลงถึง 10× และความสามารถในการผลิต layout ที่ผ่านการจำลองเชิงต่อเนื่องภายใน 24 ชั่วโมง กระบวนการ NPI (New Product Introduction) ที่เดิมอาจกินเวลาหลายเดือนสามารถย่นเหลือเป็นสัปดาห์หรือไม่กี่เดือน ทำให้ time‑to‑market ลดลงอย่างมีนัยสำคัญ สถิติภาคอุตสาหกรรมชี้ว่าอุปกรณ์ IoT และอุปกรณ์สื่อสารไร้สายยังคงเติบโตต่อเนื่อง ส่งผลให้ความต้องการการเปิดตัวรุ่นใหม่และการตอบรับตลาดแบบเร็วเป็นปัจจัยเชิงแข่งขันที่สำคัญ

ในเชิงห่วงโซ่อุปทาน การลดรอบออกแบบและการทดสอบจะส่งผลต่อการจัดการคลังสินค้าและการวางแผนการผลิตของซัพพลายเชนอย่างชัดเจน ได้แก่

- ลดความจำเป็นด้าน safety stock เนื่องจากการออกแบบและปรับปรุงทำได้รวดเร็วขึ้น จึงสามารถตอบสนองต่อความต้องการจริงได้ใกล้เคียงขึ้น

- เปลี่ยนรูปแบบการจองกำลังการผลิตของ fabs จากการสั่งผลิตเป็นล็อตใหญ่ล่วงหน้ายาวเป็นการจองแบบยืดหยุ่นและรอบสั้น ๆ ซึ่งต้องการความร่วมมือด้าน scheduling กับโรงงานผลิต

- เพิ่มบทบาทของผู้ให้บริการทดสอบภายนอก (ATE/test houses) เพื่อทำการยืนยันผลการจำลองในระดับการผลิตจริงและการวัดผลมุมมองการใช้งานจริง (real‑world performance)

ในระดับธุรกิจ ผลิตภัณฑ์เช่น Spec2Layout จะเปิดโอกาสให้เกิดโมเดลธุรกิจใหม่ ๆ สำหรับสตาร์ทอัพและผู้ให้บริการ EDA ดังนี้: บริษัทออกแบบชิป (fabless) และสตูดิโอออกแบบอาจเปลี่ยนจากการคิดค่าบริการแบบครั้งเดียวเป็นรูปแบบ AI‑assisted design as a service ที่คิดค่าบริการเป็นรายโปรเจ็กต์หรือรายเดือน ผู้ให้บริการ EDA สามารถนำเทคโนโลยีเรียนรู้เชิงลึกไปผนวกรวมเป็นโมดูลเสริมเพื่อเสนอบริการเพิ่มมูลค่า เช่น การปรับจูน RF แบบอัตโนมัติ การสร้าง IP ที่ผ่านการยืนยัน และบริการประเมินความเสี่ยงด้านการผลิต นอกจากนี้ยังมีโอกาสทางธุรกิจสำหรับสตาร์ทอัพที่เชี่ยวชาญด้านการบูรณาการระหว่างซอฟต์แวร์ AI กับการจำลองฮาร์ดแวร์เพื่อให้บริการแบบ end‑to‑end

อย่างไรก็ดี การยอมรับในระดับการผลิตจริงยังต้องการความร่วมมือเชิงลึกกับ fabs และผู้ให้บริการทดสอบเพื่อยืนยันความถูกต้องในมุมมอง process‑variation, yield และ reliability ในสเกลการผลิตจริง เช่น การจัดโปรแกรม pilot run ร่วมกับโรงงาน wafer, การทดสอบแบบ accelerated life test และการเปรียบเทียบผลกับเครื่องมือ EDA ดั้งเดิม การร่วมมือเชิงวิศวกรรมและเชิงธุรกิจเหล่านี้เป็นสิ่งจำเป็นเพื่อให้ผลลัพธ์จากโมเดลสามารถนำไปสู่การผลิตจำนวนมากได้อย่างปลอดภัยและคุ้มค่า

ผลกระทบต่อการจ้างงานและทักษะจะเป็นทั้งการเปลี่ยนแปลงและโอกาสใหม่ ๆ — ตำแหน่งงานบางส่วนที่เป็นงานเชิงปฏิบัติซ้ำ ๆ อาจถูกแทนที่ด้วยการอัตโนมัติ ขณะที่ความต้องการแรงงานที่มีทักษะผสมผสานจะเพิ่มขึ้น ได้แก่

- วิศวกร RF/Analog ที่มีความรู้ด้าน AI/ML — สามารถออกแบบ ควบคุม และปรับแต่งโมเดลร่วมกับการจำลอง SPICE เชิงต่อเนื่อง

- Data engineer / MLOps สำหรับฮาร์ดแวร์ — ดูแล pipeline ข้อมูลการออกแบบ, label ที่เกี่ยวข้องกับการวัด, และ deployment ของโมเดลในสภาพแวดล้อมการออกแบบ

- Verification & validation engineer — รับผิดชอบการสื่อสารกับ fabs และ test houses เพื่อยืนยัน yield และความน่าเชื่อถือ

สุดท้ายคือโอกาสในการขยายสู่ตลาดต่างประเทศ: เทคโนโลยีที่ลดรอบ NPI และเพิ่มความแม่นยำในวงจร RF/Analog มีความต้องการสูงในภูมิภาคที่มีห่วงโซ่อุปทานอิเล็กทรอนิกส์หนาแน่น เช่น เอเชียตะวันออกเฉียงใต้ จีน ญี่ปุ่น และสหรัฐอเมริกา การขยายออกไปสู่ต่างประเทศจำเป็นต้องมีกลยุทธ์ทางธุรกิจที่รวมทั้งการจับมือกับ fabs ในพื้นที่ การรับรองมาตรฐานสากล และการนำเสนอกรณีศึกษาที่แสดงผลการลดเวลาและต้นทุนอย่างชัดเจน เพื่อให้ผู้ผลิตระดับโลกยอมรับแพลตฟอร์มใหม่เป็นส่วนหนึ่งของกระบวนการผลิตหลัก

สรุปแล้ว Spec2Layout มีศักยภาพในการผลักดันการเปลี่ยนแปลงเชิงระบบในห่วงโซ่อุตสาหกรรมชิปและ IoT — เร่ง time‑to‑market สำหรับ OEM/ODM, เปิดโมเดลธุรกิจใหม่ให้กับผู้ให้บริการ EDA และสตาร์ทอัพ, เปลี่ยนความต้องการทักษะของแรงงาน และสร้างข้อจำเป็นในการร่วมมือกับ fabs และผู้ให้บริการทดสอบเพื่อให้การใช้งานขยายสู่ระดับการผลิตได้อย่างมั่นคง

ข้อจำกัด ความเสี่ยง และแผนพัฒนาต่อไป

ข้อจำกัดเชิงเทคนิคและความเสี่ยง

แม้ Spec2Layout ซึ่งผสานความสามารถของ Large Language Models (LLMs) กับ Differentiable‑SPICE จะทำให้การออกแบบวงจร RF/Analog เร็วขึ้นอย่างมีนัยสำคัญ แต่ยังคงมีข้อจำกัดเชิงเทคนิคที่ต้องพิจารณาอย่างรอบคอบ ได้แก่ ความแม่นยำของโมเดลเมื่อเทียบกับผลจริงบนชิป, ความคงตัวของกระบวนการ optimization ในพื้นที่พารามิเตอร์ที่ไม่เชิงเส้นสูง, และความสามารถรองรับกระบวนการผลิต (PDKs/process corners) ที่หลากหลาย เมื่อเทียบกับซิมูเลชัน SPICE แบบดั้งเดิม โมเดลเชิงดิฟเฟอเรนเชียลอาจละเลยพฤติกรรมขอบเขตบางประการ เช่น non‑ideal layout parasitics, EM coupling แบบความถี่สูง, หรือความเบี่ยงเบนจากกระบวนการผลิตจริง ซึ่งอาจนำไปสู่ความคลาดเคลื่อนของพารามิเตอร์สำคัญ (เช่น S‑parameters, noise figure, linearity) ได้

ตัวอย่างการทดสอบภายในเบื้องต้นของสตาร์ทอัพชี้ให้เห็นว่า Spec2Layout ลดรอบทดลองฮาร์ดแวร์ได้มากถึง 10× ในเคสที่มีข้อมูลเทรนนิ่งครบถ้วนและ PDK ที่รองรับครบ แต่ในกรณีที่ต้อง generalize ไปยัง fabs หรือ process node ใหม่ ๆ ความเบี่ยงเบนเฉลี่ยของพารามิเตอร์บางตัวอาจเพิ่มขึ้นถึง หลายเปอร์เซ็นต์ (ตัวอย่างเช่น S21 เบี่ยงเบน 5–15% ในชุดข้อมูลบางชุด) ซึ่งยังจำเป็นต้องนำมาพิจารณาก่อนใช้งานในผลิตภัณฑ์เชิงพาณิชย์

ความเสี่ยงจากการพึ่งพาข้อมูลเทรนนิ่งและการ generalize

- Bias ของชุดข้อมูล — ถ้าชุดข้อมูลเทรนนิ่งมาจากกลุ่ม fabs หรือเทคโนโลยีจำเพาะ โมเดลอาจ overfit กับลักษณะเฉพาะนั้นและไม่สามารถนำไปใช้ได้ตรง ๆ กับกระบวนการผลิตใหม่ ๆ

- ความไม่ต่อเนื่องของ PDK — PDK ของแต่ละ fabs มีรูปแบบ device models, corner definitions, และ DRC/LVS rules ที่ต่างกัน การขยายไปยัง PDK ใหม่จำเป็นต้องมีการแมปและปรับแต่งอย่างเป็นระบบ

- ความไม่แน่นอนและการประเมินความเชื่อมั่น — ผลลัพธ์ที่โมเดลให้มาจำเป็นต้องมาพร้อมกับตัวชี้วัดความไม่แน่นอน (uncertainty estimates) เพื่อให้วิศวกรตัดสินใจได้ว่าจำเป็นต้องทดสอบเพิ่มเติมหรือไม่

ประเด็นด้าน IP และการรักษาความลับ

งานออกแบบ RF/Analog มักมีมูลค่า IP สูง การใช้งานระบบอัตโนมัติที่พึ่งพาข้อมูลออกแบบจริงยิ่งเพิ่มความเสี่ยงด้านการรั่วไหลของข้อมูล สตาร์ทอัพต้องจัดการเรื่องนี้อย่างเข้มงวดทั้งทางเทคนิคและกฎหมาย:

- มาตรการป้องกันทางเทคนิค — ใช้การเข้ารหัสข้อมูล (at‑rest และ in‑transit), Hardware Security Modules (HSMs), และพื้นที่รันที่ปลอดภัย (secure enclaves) เพื่อป้องกันการเข้าถึงที่ไม่ได้รับอนุญาต

- การควบคุมการเข้าถึงและการตรวจสอบ — การจัดการสิทธิ์แบบละเอียด, audit logs ที่ตรวจสอบได้, และระบบแยกข้อมูลสำหรับลูกค้าแต่ละราย

- ข้อผูกมัดทางกฎหมาย — ข้อตกลง NDA, สัญญา IP assignment, และเงื่อนไขการใช้ข้อมูลที่ชัดเจน เพื่อป้องกันการใช้ข้อมูลออกแบบไปในทางที่ผิด

แผนพัฒนาต่อไปและความร่วมมือกับพันธมิตร

เพื่อบรรเทาความเสี่ยงและยกระดับความน่าเชื่อถือของ Spec2Layout สตาร์ทอัพได้วางแผนพัฒนาหลายมิติ ซึ่งรวมถึงการทำงานร่วมกับ fabs, การเพิ่มชุดทดสอบจาก third‑party, และการเสริมกระบวนการ verification อย่างเคร่งครัด:

- การขยาย PDK และการปรับแต่งต่อฟาบ — ภายใน 6–12 เดือนแรก จะเพิ่มการรองรับ PDK ของฟาบหลักอย่างน้อย 3–5 ราย โดยใช้วิธี domain adaptation และ transfer learning เพื่อลดความจำเป็นในการเทรนใหม่จากศูนย์สำหรับแต่ละฟาบ

- ชุดทดสอบ third‑party และการยืนยันผลบนชิปจริง — ร่วมมือกับห้องปฏิบัติการอิสระและผู้ให้บริการทดสอบ (ATE/measurement houses) เพื่อสร้างชุดทดสอบมาตรฐานและทำ test‑chip verification โดยมีเมตริกเช่น deviation ของ S‑parameters, NF, IIP3, และ yield ที่เป็นกลาง

- การเสริมกระบวนการ verification — นำแนวทาง verification แบบหลายชั้น (simulation-in-the-loop, silicon‑in‑the‑loop, Monte Carlo analysis, corner testing) มาใช้เป็นมาตรฐาน ก่อนอนุมัติให้ผลิตจริง นอกจากนี้จะผนวก DRC/LVS/EM checks และ EDA partner integrations เพื่อให้ flow สอดคล้องกับกระบวนการผลิต

- การพัฒนาโมเดลและความเสถียรของ optimization — ปรับปรุง loss functions, ใช้ ensemble models และ regularization techniques เพื่อลดความผันผวนของ optimization และเพิ่มความทนทานต่อ local minima รวมทั้งเพิ่มกลไก quantification ของ uncertainty เพื่อให้วิศวกรสามารถตีความผลออกแบบได้ดีขึ้น

- มาตรฐานความปลอดภัยและการปฏิบัติตามข้อกำหนด — มุ่งเป้าเพื่อการรับรองเช่น ISO 27001 และ SOC 2 ในระยะกลาง พร้อมกับการนำแนวปฏิบัติด้าน data governance และ supply chain security มาใช้จริง

- รูปแบบความร่วมมือเชิงพาณิชย์ — เสนอโปรแกรม pilot ร่วมกับ fabs และลูกค้าเป้าหมาย โดยให้บริการแบบ on‑premise หรือ hybrid เพื่อรองรับความต้องการด้านความลับของลูกค้าที่แตกต่างกัน

โดยสรุป Spec2Layout มีศักยภาพในการลดรอบการพัฒนาฮาร์ดแวร์และเร่งนวัตกรรม แต่ต้องยอมรับความซับซ้อนและความเสี่ยงเชิงเทคนิคที่มาพร้อมกัน เพื่อให้สามารถนำไปใช้ในแวดวงอุตสาหกรรมได้อย่างมั่นคงและปลอดภัย การลงทุนใน PDK coverage, การทดสอบ third‑party ที่เป็นกลาง, มาตรการรักษาความปลอดภัยของ IP และการรับรองมาตรฐานเชิงปฏิบัติจะเป็นกุญแจสำคัญของแผนพัฒนาต่อไป

เสียงจากผู้ก่อตั้งและนักวิเคราะห์ (ตัวอย่างคำพูด)

เสียงจากผู้ก่อตั้งและนักวิเคราะห์ (ตัวอย่างคำพูด)

ผู้ก่อตั้ง — ดร.สมชาย วัฒนา, CEO "วิสัยทัศน์ของเราคือการยกระดับกระบวนการออกแบบ RF/Analog จากเดิมที่ใช้เวลาเป็นสัปดาห์หรือเป็นเดือน ให้กลายเป็นกระบวนการที่ผู้เชี่ยวชาญและทีมพัฒนาทั่วไปสามารถเข้าถึงได้ภายใน 24 ชั่วโมง ด้วยการผสาน LLM กับ Differentiable‑SPICE เราเห็นการลดรอบทดลองฮาร์ดแวร์ได้มากถึง 10× ในโปรเจกต์นำร่องบางราย ซึ่งหมายถึงการลดต้นทุนการพัฒนาและ Time‑to‑Market อย่างชัดเจน สำหรับโมเดลธุรกิจ เราวางรูปแบบเป็น SaaS แบบสมัครสมาชิกรายองค์กร ผสานกับระบบเครดิตต่อการรันการจำลอง และบริการให้คำปรึกษาแยกต่างหากสำหรับการปรับ PDK และการยืนยันผลในโรงงาน"

ผู้ร่วมก่อตั้งฝ่ายเทคนิค — น.ส.ปัทมา เกียรติยศ, Head of Engineering "เราออกแบบสถาปัตยกรรมให้รองรับการเชื่อมต่อกับ PDK ของผู้ผลิตหลายรายและสามารถรันแบบจำลองหลายระดับ (multi‑fidelity) ได้ใน pipeline เดียว ผลลัพธ์ที่ได้ไม่ใช่ 'การแทนที่' SPICE แต่เป็นการเร่งวงจรสำรวจพารามิเตอร์ (design space exploration) ทำให้วิศวกรสามารถจำกัดขอบเขตและส่งแบบที่มีโอกาสผ่านการทดสอบสูงขึ้นไปยังเวิร์กโฟลว์ฮาร์ดแวร์ ภาพรวมคือเพิ่ม productivity ของทีมออกแบบ 2–5× ในช่วงต้น และลดจำนวนการเทสต์จริงในภาคสนามได้อย่างมีนัยสำคัญ"

วิศวกรทดสอบระบบ — นายวิทยา ภูมิศักดิ์, RF Engineer (ลูกค้ากลุ่มนำร่อง) "ในการทดสอบจริง เราพบว่าอินเทอร์เฟซที่เป็นธรรมชาติและการตั้งค่าอัตโนมัติช่วยลดขั้นตอนที่ซับซ้อน เช่น การเทียบ PDK และการตั้ง bias ด้วยตนเอง อย่างไรก็ตามยังมีข้อจำกัดบางอย่าง เช่น แบบจำลองสำหรับ non‑linear behavior ที่ความถี่สูงมากหรือสภาวะอิ่มตัวยังต้องการการปรับด้วยมือ และบางกรณีต้องมี human‑in‑the‑loop เพื่อยืนยันความถูกต้องก่อนส่งไปผลิตจริง แต่โดยรวมแล้ว รอบการทดลองฮาร์ดแวร์ลดลงจากเฉลี่ย 8–12 ครั้งต่อฟังก์ชัน เหลือ 1–2 ครั้งในหลายกรณี"

นักวิเคราะห์อุตสาหกรรม — ดร.มาริน ทองเจริญ, Senior Analyst, TechMarket Insights "เทคโนโลยีที่ผสาน LLM กับ Differentiable‑SPICE และการเรียนรู้เชิงตัวแบบ (differentiable modeling) ถือเป็นจุดเปลี่ยนสำหรับวงการออกแบบอนาล็อกและ RF ยุคใหม่ นักลงทุนควรพิจารณา 1) ความสามารถในการปกป้องทรัพย์สินทางปัญญาและเทคโนโลยี (IP), 2) ความเข้ากันได้กับ ekosystem ของ EDA และ fabs, 3) กลยุทธ์การหารายได้ที่ชัดเจน เช่น model licensing + professional services เพื่อสร้างรายได้ซ้ำได้ นอกจากนี้ การพิสูจน์ผลบนโปรเจกต์เชิงพาณิชย์ (commercial pilots) ยังเป็นกุญแจสำคัญก่อนการขยายตลาดวงกว้าง"

นักวิเคราะห์ด้านการลงทุน — น.ส.กมลวรรณ สุขเกษม, Venture Partner "เมื่อตัดสินใจลงทุน เรามองตัวชี้วัดหลักคือ 'unit economics' ของการให้บริการจำลอง, อัตราการรักษาลูกค้า (customer retention) และการขยายสัญญากับลูกค้าองค์กร (enterprise expansion). สตาร์ทอัพที่สามารถแสดงผลลัพธ์เช่นการลดเวลาออกแบบ 24 ชั่วโมงและลดรอบฮาร์ดแวร์ 10× จะมีความน่าสนใจสูง แต่นักลงทุนนิยมเห็นการประเมินความเสี่ยงด้านการปรับใช้จริง เช่น การรับรองแบบในมาตรฐานอุตสาหกรรม และการจัดการข้อมูลที่อ่อนไหวของลูกค้า"

คำแนะนำสำหรับบริษัทที่สนใจทดลองใช้งาน

- เริ่มด้วยโครงการนำร่องขนาดเล็ก: เลือกโมดูลหรือฟังก์ชันที่มีความเสี่ยงต่ำและวัดผลเป็นตัวชี้วัดที่ชัดเจน เช่น เวลาออกแบบ, จำนวนรอบฮาร์ดแวร์, และอัตราสำเร็จของการทดสอบ

- ตั้งทีมร่วมงาน (cross‑functional pilot team): ประกอบด้วยวิศวกรฮาร์ดแวร์, วิศวกรซอฟต์แวร์, และผู้เชี่ยวชาญด้าน PDK เพื่อประกันการผสานงานและลดช่องว่างความเข้าใจ

- ตรวจสอบการปฏิบัติตามข้อกำหนดด้านความปลอดภัยข้อมูล: โดยเฉพาะการจัดการ PDK และข้อมูลเซนซิทีฟของลูกค้า ควรมีข้อตกลง NDA และมาตรการ encryption ในการส่งข้อมูล

- วางแผนการยืนยันผล (validation roadmap): กำหนดขั้นตอนยืนยันผลแบบ incremental ตั้งแต่ simulation fidelity สูงสุดจนถึงการวัดบนฮาร์ดแวร์จริง

- ประเมินโมเดลธุรกิจร่วมกัน: พิจารณาโมเดลการจ่ายเงินแบบใช้งานจริง (pay‑per‑run), subscription สำหรับการสนับสนุนระยะยาว และบริการปรับแต่ง PDK เพื่อสร้างรายได้เสริม

สรุป — เสียงจากผู้ก่อตั้ง วิศวกร และนักวิเคราะห์สะท้อนมุมมองเชิงบวกต่อศักยภาพของ Spec2Layout ในการย่นระยะเวลาและต้นทุนของการออกแบบ RF/Analog แต่ยังเตือนให้เตรียมมาตรการด้านวิศวกรรมและการจัดการความเสี่ยงก่อนการขยายสู่การผลิตจริง การทดลองเชิงพาณิชย์ที่มีการวัดผลชัดเจนและการร่วมมือกับพันธมิตรในระบบนิเวศจะเป็นกุญแจสำคัญสู่ความสำเร็จในระดับอุตสาหกรรม"

บทสรุป

Spec2Layout ของสตาร์ทอัพไทยเป็นตัวอย่างที่ชัดเจนของการผสานระหว่างโมเดลภาษาใหญ่ (LLM) กับการจำลองเชิงฟิสิกส์แบบ differentiable‑SPICE เพื่อเร่งกระบวนการออกแบบวงจร RF/Analog โดยรายงานระบุว่าสามารถสร้างเลย์เอาต์เริ่มต้นได้ภายใน 24 ชั่วโมงและลดรอบการทดลองฮาร์ดแวร์ได้ประมาณ 10× ซึ่งหมายความว่าเวลาในการทดลองและปรับปรุงต้นแบบเชิงกายภาพอาจลดลงอย่างมีนัยสำคัญ ส่งผลให้ต้นทุน การใช้ทรัพยากร และเวลาในการขึ้นผลิตภัณฑ์เข้าสู่ตลาด (time‑to‑market) ดีขึ้น ตัวอย่างเช่น การผสานความสามารถในการเรียนรู้เชิงสัญลักษณ์ของ LLM กับกราฟและความต่อเนื่องของ SPICE ช่วยให้การสำรวจพื้นที่พารามิเตอร์ (design space) ทำได้รวดเร็วขึ้นและมีแนวโน้มลดจำนวนรอบการซ่อมแซมและการทดสอบบนบอร์ดจริง

อย่างไรก็ดี ตัวเลขเช่น “24 ชั่วโมง” และการลดรอบฮาร์ดแวร์ 10× ถึงจะน่าดึงดูด แต่ยังต้องการการตรวจสอบเชิงอิสระและการพิสูจน์ในสภาพแวดล้อมการผลิตจริงก่อนยืนยันศักยภาพในเชิงอุตสาหกรรม การทดสอบเพิ่มเติมควรรวมถึงการร่วมมือกับ fabs และการใช้ PDK/เทคโนโลยีหลายโหนด (เช่น CMOS ที่ต่างกัน) การยืนยันผลในระดับการผลิตต้องตอบคำถามเรื่องความทนทาน ผลผลิต (yield) พฤติกรรมระยะยาว (aging/thermal) และความเที่ยงตรงของการจำลองเมื่อเทียบกับการวัดจริง ในเชิงอนาคต หากมีการพิสูจน์และบูรณาการกับเครื่องมือ EDA, กระบวนการรับรอง และห่วงโซ่อุปทานของผู้ผลิตอย่างเป็นระบบ Spec2Layout อาจเปลี่ยนโฉมการออกแบบ RF/Analog ให้เป็นการทำงานแบบไฮบริดระหว่างมนุษย์และ AI ที่รวดเร็วและมีประสิทธิภาพยิ่งขึ้น แต่เส้นทางสู่การยอมรับในระดับอุตสาหกรรมยังต้องผ่านการตรวจสอบ การทดลองภาคสนาม และความร่วมมือเชิงนโยบายและเชิงพาณิชย์เพิ่มเติม