ข่าวการประกาศเปิดตัวชิปของ Arm ถือเป็นจุดเปลี่ยนสำคัญที่อาจเขย่าตลาดเซมิคอนดักเตอร์ทั่วโลก: จากบทบาทเดิมในฐานะผู้ออกแบบสถาปัตยกรรมซีพียูที่ถูกใช้งานในสมาร์ทโฟนกว่า 90% ของโลก กลายเป็นผู้เล่นที่ลงมาผลิตชิปเองโดยตรง เหตุการณ์นี้ไม่น้อยไปกว่าการพลิกโฉมโครงสร้างอุตสาหกรรม ตั้งแต่ตลาดมือถือที่ Arm ครองตำแหน่งสำคัญ ไปจนถึงตลาดเซิร์ฟเวอร์ที่กำลังขยายตัวผ่านโซลูชันอย่าง Apple M-series และ AWS Graviton — ทั้งหมดนี้ชี้ให้เห็นว่าการแข่งขันทางเทคโนโลยีและห่วงโซ่อุปทานจะร้อนแรงยิ่งขึ้น

บทความนี้จะพาอ่านวิเคราะห์เชิงลึกว่าแผนการของ Arm จะส่งผลอย่างไรทั้งในแง่เทคนิค การแข่งขันระหว่างผู้ผลิตชิป การจัดการซัพพลายเชนระดับโลก รวมถึงโอกาสเชิงกลยุทธ์ที่อุตสาหกรรมสามารถคว้าได้ ตัวอย่างที่ชัดเจนคือการเปลี่ยนจากการให้สิทธิ์สถาปัตยกรรม (IP licensing) ไปสู่การเป็นผู้ผลิตจริง ซึ่งอาจกระทบทั้งผู้ผลิตไอโซเลชัน (foundry), ลูกค้า OEM และพันธมิตรด้านซอฟต์แวร์—บทนำนี้จะเป็นกรอบนำทางก่อนที่เราจะลงลึกในประเด็นทางเทคนิค ผลกระทบทางเศรษฐกิจ และกลยุทธ์การแข่งขันที่ตามมา

บทนำ: ข่าวสำคัญและความหมายเชิงกลยุทธ์

บทนำ: ข่าวสำคัญและความหมายเชิงกลยุทธ์

Arm ประกาศในแถลงการณ์ล่าสุดว่าองค์กรจะเข้าสู่ธุรกิจการออกแบบชิปเป็นผู้ผลิตชิปภายใต้แบรนด์ของตนเอง นับเป็นการเปลี่ยนทิศทางที่สำคัญจากโมเดลธุรกิจดั้งเดิมซึ่งมุ่งเน้นการออกแบบสถาปัตยกรรมและการให้สิทธิ์ (IP/licensing) แก่ผู้ผลิตชิปและผู้พัฒนาระบบแบบต่าง ๆ มาเป็นการลงมือพัฒนาชิปจริงเพื่อนำออกสู่ตลาดโดยตรง การประกาศนี้วางตำแหน่ง Arm จากผู้ให้สถาปัตยกรรมเชิงกลางสู่ผู้เล่นเชิงผลิตภัณฑ์ที่มีความสามารถในการแข่งขันด้านชิปอย่างชัดเจน

ความแตกต่างจากโมเดลเดิม – ภายใต้โมเดลเดิม Arm ทำรายได้หลักจากการให้สิทธิ์และค่าลิขสิทธิ์ (royalties) แก่พันธมิตรที่นำสถาปัตยกรรมของ Arm ไปออกแบบเป็นชิป เช่น สมาร์ทโฟน อุปกรณ์ฝังตัว และเซิร์ฟเวอร์ ทำให้ Arm ทำหน้าที่เป็นผู้ให้มาตรฐานและเทคโนโลยีแก่อุตสาหกรรม ในขณะที่การประกาศล่าสุดระบุว่า Arm จะออกแบบและนำเสนอชิปของตนเอง ซึ่งเป็นการขยายห่วงโซ่คุณค่าไปสู่การพัฒนาผลิตภัณฑ์และการจัดจำหน่ายที่มีความเสี่ยงและโอกาสทางการเงินต่างจากการให้สิทธิ์โดยสิ้นเชิง

ความหมายเชิงกลยุทธ์ – การก้าวสู่การเป็นผู้ผลิตชิปโดยตรงมีนัยสำคัญหลายด้าน: ทั้งโอกาสในการเพิ่มมาร์จิ้น รายได้จากการขายผลิตภัณฑ์ปลายทาง และการควบคุมซัพพลายเชนและการออกแบบอย่างลึกซึ้งยิ่งขึ้น แต่พร้อมกันนั้นยังหมายถึงการเผชิญหน้ากับลูกค้าปัจจุบันที่เคยเป็นผู้รับใบอนุญาตของ Arm ซึ่งอาจมองว่า Arm กลายเป็นคู่แข่ง นอกจากนี้ยังเพิ่มความเสี่ยงด้านการลงทุนและการปฏิบัติการ เช่น ความต้องการด้านการผลิต การรับประกันคุณภาพ และการบริการหลังการขาย รวมถึงแรงกดดันด้านกฎระเบียบและการแข่งขันทางการค้า ที่อาจตามมา

ไทม์ไลน์สั้น ๆ จากแถลงการณ์เผยให้เห็นลำดับการดำเนินการเชิงยุทธศาสตร์:

- ประกาศเชิงนโยบายและกลยุทธ์แก่ผู้ถือหุ้นและสื่อ

- เปิดเผยแนวทางการออกแบบชิปและการใช้ IP ของ Arm เป็นฐาน

- ระบุแผนความร่วมมือกับพันธมิตรด้านการผลิต (foundries) และซัพพลายเชน

- ระบุกรอบเวลาสำหรับการสาธิตหรือการส่งชิ้นงานตัวอย่างแก่พันธมิตรและลูกค้า

การตอบรับเบื้องต้นจากตลาดเป็นไปในลักษณะผสมผสาน: นักลงทุนและนักวิเคราะห์มองเห็น โอกาสในการขยายแหล่งรายได้และมาร์จิ้น แต่ก็ชี้ถึงความท้าทายเชิงปฏิบัติการและความเสี่ยงต่อความสัมพันธ์กับลูกค้าที่เป็นคู่ค้าเดิม บางเสียงจากนักวิเคราะห์ชี้ว่าแผนนี้อาจเพิ่มมูลค่าระยะยาวหาก Arm สามารถแสดงความเหนือชั้นด้านประสิทธิภาพและการผลิตได้จริง ขณะที่นักวิเคราะห์อีกกลุ่มเตือนถึง ความเสี่ยงด้านการแย่งชิงส่วนแบ่งตลาดและปัญหาการปรับสมดุลกับลูกค้า ซึ่งอาจนำไปสู่แรงกดดันทางราคาหรือการเลือกพันธมิตรที่หลีกเลี่ยงการใช้ชิป Arm ในบางกรณี

ตัวอย่างคำพูดจากผู้บริหารที่บริษัทสื่อออกมาในแถลงการณ์ (สรุปเชิงใจความ) ระบุว่า บริษัทมองว่าการออกแบบชิปเองเป็น “การขยายบทบาทเชิงยุทธศาสตร์เพื่อตอบโจทย์ตลาดใหม่ ๆ และเร่งสร้างนวัตกรรมให้กับระบบนิเวศของ Arm” ขณะเดียวกันผู้บริหารก็ย้ำว่า Arm จะยังคงรักษาความสัมพันธ์กับพันธมิตรและลูกค้าเดิมเป็นสิ่งสำคัญ

โดยสรุป การประกาศของ Arm ครั้งนี้เป็นจุดเปลี่ยนเชิงกลยุทธ์ที่อาจเขย่าระบบนิเวศของผู้ผลิตชิป — เปิดโอกาสให้เกิดการแข่งขันและนวัตกรรมใหม่ ๆ แต่ก็ทดสอบความสมดุลระหว่างการเป็นผู้ให้เทคโนโลยีที่เป็นกลางกับการเป็นผู้แข่งขันเชิงผลิตภัณฑ์อย่างจริงจัง

สเปกทางเทคนิคและสถาปัตยกรรมของชิป Arm

สรุปภาพรวมสถาปัตยกรรมและรุ่นที่ประกาศ

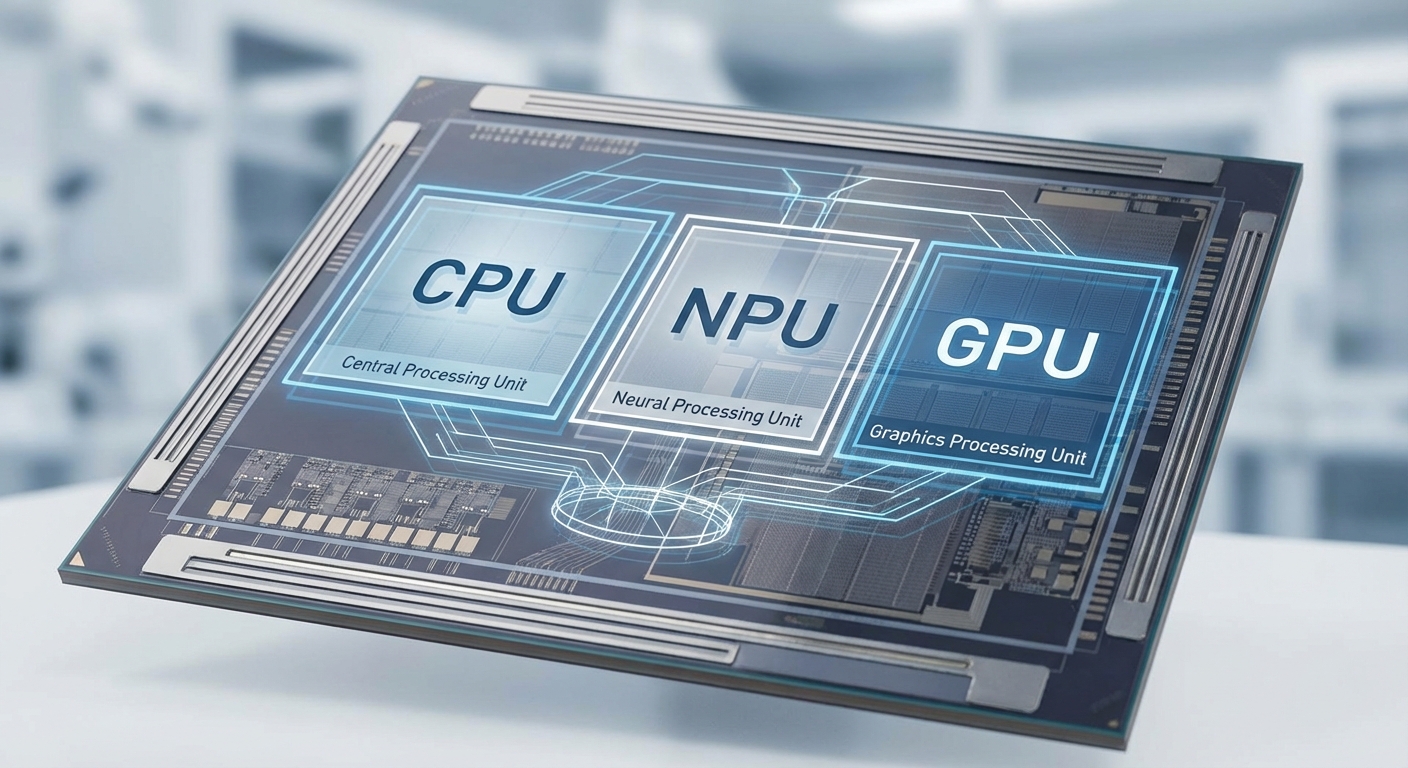

Arm ประกาศชุดชิปของตนเองภายใต้ซีรีส์หลักซึ่งบริษัทระบุชื่อรุ่นเป็นการตลาดว่า Arm Aurora (รุ่นเรือธงสำหรับอุปกรณ์ประสิทธิภาพสูง) และ Arm Boreal (รุ่นกลางสำหรับสมาร์ทโฟนและอุปกรณ์ edge) โดยทั้งสองซีรีส์ออกแบบมาในแนวทาง System-on-Chip (SoC) แบบโมดูลาร์ ประกอบด้วยองค์ประกอบสำคัญ ได้แก่ CPU, NPU, GPU และ ISP ซึ่ง Arm ระบุว่าจะผลิตบนกระบวนการที่แตกต่างกันตามระดับรุ่นคือ 3nm สำหรับรุ่นเรือธง (Aurora) และ 5nm สำหรับรุ่นระดับกลาง (Boreal) เพื่อให้ได้ความสมดุลระหว่างประสิทธิภาพและการประหยัดพลังงาน

สถาปัตยกรรมคอร์และองค์ประกอบบนชิป (CPU, NPU, GPU, ISP)

- CPU: ซีรีส์ Aurora ใช้สถาปัตยกรรมแบบ Heterogeneous multi-core ประกอบด้วยคอร์ประสิทธิภาพสูง (performance cores) แบบใหม่ที่ Arm ระบุว่าเป็นการยกระดับ microarchitecture ของ Cortex-X พร้อมคอร์ประหยัดพลังงาน (efficiency cores) สำหรับงาน background และ multitasking การออกแบบรองรับ cluster แบบ 2+6 หรือ 4+4 ขึ้นกับการปรับแต่งของผู้ผลิต

- NPU (Neural Processing Unit): Arm เปิดตัวโมดุล NPU คู่ชื่อตามการตลาดว่า Helios-N สำหรับ Aurora และเวอร์ชันย่อสำหรับ Boreal โดยตัวเรือธงบนกระบวนการ 3nm ประกาศสเปกสูงสุดที่ ประมาณ 200 TOPS (INT8 peak) ในขณะที่เวอร์ชัน 5nm ของ Boreal อยู่ราว 60–80 TOPS (ตัวเลขเป็นค่า peak ที่ Arm ให้เป็นข้อมูลเบื้องต้น)

- GPU: GPU ถูกออกแบบให้รองรับการเร่งกราฟิกแบบ modern mobile GPU pipeline รวมถึงคุณสมบัติ ray-tracing ในฮาร์ดแวร์ (สำหรับรุ่นเรือธง) Arm ระบุการเพิ่มประสิทธิภาพด้าน throughput ประมวลผลกราฟิกขึ้นประมาณ +25–35% เมื่อเทียบกับ generation ก่อนหน้า โดยมีตัวเลข FP32/TEX throughput ที่เพียงพอสำหรับเกมระดับสูงและการเรนเดอร์ UI ที่ราบรื่น

- ISP (Image Signal Processor): ISP ของ Aurora รองรับกล้องความละเอียดสูงสูงสุดถึง 200MP และการประมวลผลวิดีโอ 8K ที่ 60fps พร้อมฟีเจอร์ถ่ายภาพ computational photography แบบเรียลไทม์ (HDR fusion, multi-frame denoise) ซึ่งใช้ NPU ในการเร่งการทำงานบางส่วน

ตัวเลขประสิทธิภาพที่ Arm เปิดเผยและการเปรียบเทียบเบื้องต้น

Arm ให้ตัวเลขเปรียบเทียบเชิงเบื้องต้นดังนี้: IPC (Instructions per cycle) ของคอร์ประสิทธิภาพสูงในรุ่น Aurora เพิ่มขึ้นราว 25–30% เมื่อเทียบกับสถาปัตยกรรมก่อนหน้าใน workload ประเภท single-threaded และ mixed integer/float workloads สำหรับ NPU, Arm ระบุว่า Helios-N ในรุ่น 3nm สามารถทำได้สูงสุด ~200 TOPS (INT8) โดยมีตัวเลขประสิทธิภาพต่อวัตต์ (efficiency) อยู่ที่ประมาณ 20–25 TOPS/W ในสภาวะการใช้งานบางกรณี ขณะที่เวอร์ชัน 5nm จะให้ TOPS ต่ำกว่าแต่ยังคงมีประสิทธิภาพต่อวัตต์ที่ดี

สำหรับ GPU Arm อ้างว่าประสิทธิภาพรวมของซีรีส์ Aurora เพิ่มขึ้น ~30% ใน workload สไตล์เกมและกราฟิก 3D เมื่อเทียบกับรุ่นก่อนหน้า โดย throughput ที่บริษัทยกตัวอย่างไว้สำหรับ rendering และ AI-augmented graphics จะแสดงประสิทธิภาพที่ดีขึ้นทั้งในแง่ latency และ sustained performance (ตัวอย่างเช่น benchmark แบบ GPU-bound ในสภาพ thermal equilibrium จะเห็นการลด throttling ประมาณ 15–20%)

ข้อได้เปรียบด้านการบริโภคพลังงานและการปรับใช้ในอุปกรณ์หลากหลาย

หนึ่งในประเด็นที่ Arm เน้นคือการประหยัดพลังงานจากการย้ายไปใช้ node 3nm สำหรับรุ่นเรือธงซึ่งช่วยให้ได้ทั้งประสิทธิภาพสูงและ efficiency ที่ดีขึ้น Arm ระบุว่า Aurora บน 3nm จะมีข้อได้เปรียบด้านพลังงานเมื่อเทียบกับชิป 5nm ของตนเองหรือคู่แข่งประมาณ 20–40% ขึ้นกับ workload โดยเฉพาะงาน ML inference ที่สามารถย้ายไปทำบน NPU ได้อย่างมีประสิทธิภาพกว่า CPU/GPU แบบดั้งเดิม

การปรับใช้: ในเชิงการใช้งานจริง Arm มองว่า Aurora จะตอบโจทย์ทั้ง smartphones ชั้นสูง, thin-and-light laptops ที่ต้องการ balance ระหว่าง performance กับ battery life, และอุปกรณ์ edge server ขนาดเล็กที่ต้องการการประมวลผล AI แบบ on-device ด้วย latency ต่ำ ตัวอย่างเชิงตัวเลขที่ Arm ยกขึ้น ได้แก่การรันโมเดล object detection ขนาดกลาง (เช่น MobileNet-v3 / YOLO-lite) บน NPU รุ่นเรือธงที่ระบุสามารถลด latency ลงเหลือ ~10–30 ms ต่อภาพและใช้พลังงานเพียงเศษของวัตต์ในโหมดประหยัด (ขณะที่การรันบน CPU อาจกินเวลาและพลังงานมากกว่า 3–5 เท่า)

สรุปแล้ว สเปกที่ Arm เปิดเผยเน้นที่การผสานระหว่างสถาปัตยกรรมคอร์แบบใหม่, NPU กำลังสูง, GPU ที่ปรับปรุง throughput และ ISP สำหรับการถ่ายภาพขั้นสูง พร้อมกับการผลิตบน 3nm/5nm เพื่อให้ได้ทั้งประสิทธิภาพและประหยัดพลังงาน ซึ่งส่งสัญญาณว่า Arm มุ่งหวังให้ชิปของตนสามารถแข่งขันในหลายตลาดได้ตั้งแต่สมาร์ทโฟนไปจนถึงอุปกรณ์ edge และโน้ตบุ๊กแบบบางเบา

ผลกระทบต่อการแข่งขัน: ใครได้ ใครเสีย

ผลกระทบต่อการแข่งขัน: ใครได้ ใครเสีย

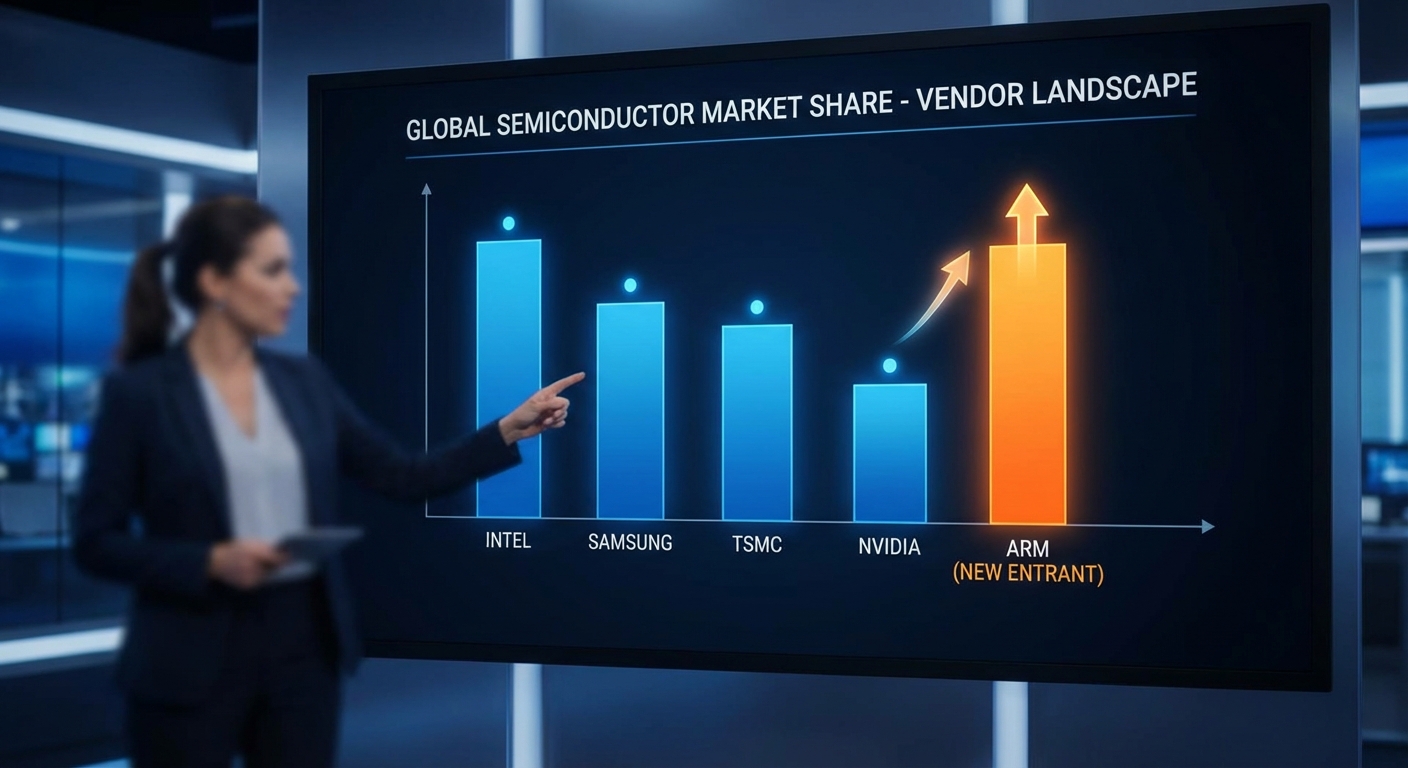

การที่ Arm ประกาศเปิดตัวชิปของตัวเองจะเป็นจุดเปลี่ยนสำคัญที่มีผลต่อสมดุลอำนาจในอุตสาหกรรมชิป โดยเฉพาะเมื่อพิจารณาว่า สถาปัตยกรรม Arm ถูกใช้งานในอุปกรณ์มือถือกว่า 90% และเป็นแกนกลางของอุปกรณ์ฝั่ง edge/IoT จำนวนมาก การเคลื่อนตัวจากโมเดลธุรกิจแบบเดิม (การให้ใบอนุญาต IP และรับค่าลิขสิทธิ์) มาสู่การขายชิปสำเร็จรูปโดยตรง อาจทำให้เกิด การแย่งชิงส่วนแบ่งตลาด และการเปลี่ยนแปลงห่วงโซ่อุปทานอย่างมีนัยสำคัญ

ในภาพรวมระยะสั้น (12–18 เดือน) ผลกระทบต่อผู้เล่นหลักจะยังไม่รุนแรงจนเปลี่ยนตำแหน่งผู้นำทันที แต่จะกดดันในเชิงราคาและมาร์จิ้น โดยเฉพาะในเซ็กเมนต์มิด-เรนจ์และอุปกรณ์ IoT ที่มักเน้นต้นทุน-ประสิทธิภาพเป็นหลัก

- Qualcomm & MediaTek: ปัจจุบัน MediaTek และ Qualcomm แบ่งส่วนแบ่งตลาดชิปสำหรับสมาร์ทโฟนระดับโลกอยู่ในสัดส่วนประมาณ MediaTek ~40–45% และ Qualcomm ~30–35% (โดยประมาณ ขึ้นกับภูมิภาคและปี) การที่ Arm ออกชิปสำเร็จรูปอาจดึงส่วนของอุปกรณ์ระดับกลางที่ไม่ต้องการปรับแต่งมากนักไปได้บางส่วน ทำให้ผู้ผลิต SoC เหล่านี้ยอมลดราคาเร่งลงทุน R&D หรือเร่งจับคู่องค์ประกอบเฉพาะทางเพื่อตอบโต้

- Apple & Samsung: ทั้งสองรายมีความสามารถในการออกแบบชิปภายใน (vertical integration) อยู่แล้ว — Apple ใช้ Apple Silicon ที่พัฒนาบนสถาปัตยกรรม Arm และมีสถานะแข็งแรงในตลาดพรีเมียม ดังนั้น Apple มีแนวโน้มได้ประโยชน์น้อยจากการที่ Arm ขายชิปโดยตรง แต่จะติดตามแผนและอาจใช้โอกาสนี้เพื่อทบทวนเงื่อนไขการอนุญาตหรือสร้างความร่วมมือเชิงยุทธศาสตร์กับ Arm ส่วน Samsung อาจรับหรือแข่งขันกับการนำเสนอของ Arm ขึ้นกับความสอดคล้องกับไลน์ผลิตภัณฑ์ Exynos และความสัมพันธ์กับผู้ผลิตชิปจากภายนอก

- Intel, AMD, NVIDIA: สำหรับตลาดพีซีและเซิร์ฟเวอร์ อิทธิพลของ Arm ที่เพิ่มขึ้นอาจทำให้การแข่งขันด้านสถาปัตยกรรมมีความเข้มข้นมากขึ้น — ปัจจุบัน x86 ยังคงมีสัดส่วนใหญ่ในเซิร์ฟเวอร์และพีซี แต่ Arm กำลังขยายบทบาทในคลาวด์ (เช่น AWS Graviton) และ edge AI หาก Arm สามารถนำเสนอชิปที่แข่งขันได้ในแง่ประสิทธิภาพต่อวัตต์และต้นทุน อาจซึมเข้าสู่ตลาดบางส่วนซึ่งกดดันผู้ผลิต x86 ให้เร่งพัฒนา หรือขยายพอร์ตโฟลิโอไปยังการเร่งความสามารถ AI

- ผู้ให้บริการคลาวด์ (AWS, Microsoft, Google): ผู้ให้บริการคลาวด์บางรายมีแนวโน้มได้ประโยชน์จากการมีตัวเลือกฮาร์ดแวร์มากขึ้น — AWS ระบุถึงการลดต้นทุนเมื่อใช้ Graviton ได้ราว 20–40% ในงานบางประเภท หาก Arm ขายชิปตรงและสามารถให้ประสิทธิภาพ/ต้นทุนที่ดี ผู้ให้บริการคลาวด์อาจขยายการนำ Arm-based instances มาใช้ ส่งผลให้สัดส่วนการประมวลผลบน Arm ในคลาวด์ค่อย ๆ เพิ่มจากระดับปัจจุบันที่ยังอยู่ในหลัก 5–10% สำหรับการใช้งานบางกรณี ไปสู่ระดับสูงขึ้นในระยะกลาง

ระยะกลาง (2–5 ปี) จะเป็นช่วงที่การชิงส่วนแบ่งตลาดชัดขึ้น: หาก Arm ลงทุนหนักในไลน์ผลิตที่ออกแบบมาแข่งขันได้จริงในแง่ IPC, NPU และตัวเร่ง AI ระดับ edge/คลาวด์ Arm อาจตัดชิ้นส่วนตลาดจากผู้ผลิต SoC รายอื่น ๆ ในสัดส่วน ประมาณ 5–15% ในตลาดอุปกรณ์ระดับกลางและ edge และอาจค่อย ๆ ขยายในตลาดเซิร์ฟเวอร์ได้อีก 2–8% ขึ้นกับการยอมรับของผู้ให้บริการคลาวด์และความสามารถของชิป

สำหรับผู้ชนะและผู้แพ้โดยสรุป: ผู้ชนะชั่วคราว ได้แก่ ผู้ให้บริการคลาวด์ที่เน้นต้นทุน-ประสิทธิภาพและผู้ผลิตอุปกรณ์ที่ต้องการตัวเลือกสำเร็จรูปเพื่อลดเวลาออกสู่ตลาด ส่วน ผู้แพ้ที่เสี่ยง ได้แก่ ผู้ผลิต SoC ที่พึ่งพิงการขายชิปมาตรฐานในเซ็กเมนต์ที่มีการแข่งขันด้านราคาโดยตรง อย่างไรก็ตาม ผู้เล่นใหญ่เช่น Qualcomm, Intel, NVIDIA และ Samsung มีช่องทางตอบโต้หลายทาง เช่น การหาพันธมิตรด้านการผลิต (TSMC/Samsung Foundry), เพิ่มการลงทุน R&D, หันสู่บริการซอฟต์แวร์และโซลูชันครบวงจร หรือเข้าซื้อกิจการเพื่อลดช่องว่าง

สุดท้ายต้องคำนึงถึงผลกระทบต่อห่วงโซ่อุปทาน: การที่ Arm ขายชิปโดยตรงจะเปลี่ยนบทบาทจากผู้ให้ IP เป็นผู้แข่งขันตรงกับลูกค้าบางราย ซึ่งอาจนำไปสู่ ความตึงเครียดทางการค้า, การปรับสัญญาไลเซนซ์, และความกังวลด้านการผูกขาด—ซึ่งอาจถูกตรวจสอบโดยหน่วยงานกำกับดูแลในบางภูมิภาค การจัดหาโรงงานผลิต (TSMC, Samsung Foundry) และการจัดสรรวัตถุดิบจะเป็นปัจจัยสำคัญ หาก Arm สามารถบริหารจัดการห่วงโซ่อุปทานได้ดี ก็มีศักยภาพที่จะสร้างแรงกดดันต่อคู่แข่งได้อย่างแท้จริงในระยะกลาง

ระบบนิเวศ (Ecosystem) และพันธมิตรที่สำคัญ

ระบบนิเวศ (Ecosystem) และพันธมิตรที่สำคัญ

การที่ Arm ตัดสินใจเข้าสู่การผลิตชิปเป็นผู้ผลิตโดยตรง มีผลต่อระบบนิเวศของผู้พัฒนาและพันธมิตรเชิงลึก ทั้งในมิติของซอฟต์แวร์ ฮาร์ดแวร์ และการให้บริการคลาวด์ ในระดับกว้าง การเคลื่อนไหวนี้จะเร่งให้เกิดความจำเป็นในการประสานงานกับกลุ่มผู้พัฒนาซอฟต์แวร์โอเพนซอร์ส เช่น ชุมชนเคอร์เนลลินุกซ์ (Linux kernel), โครงการคอมไพเลอร์อย่าง LLVM/GCC, และไลบรารีด้าน AI/ML เช่น TensorFlow, PyTorch, cuDNN ทางฝั่งผู้ผลิตซอฟต์แวร์อิสระ (ISV) จะต้องวางแผนการทดสอบและปรับแต่งแอพพลิเคชันให้เข้ากับสถาปัตยกรรมใหม่ของ Arm เพื่อให้ได้ประสิทธิภาพและความเสถียรเทียบเท่าหรือเหนือกว่าคู่แข่ง

ความจำเป็นของความร่วมมือกับผู้ผลิตซอฟต์แวร์และชุมชนโอเพนซอร์ส เป็นปัจจัยสำคัญในการสร้างความเชื่อมั่นให้กับตลาดและลูกค้าองค์กร การนำชิปใหม่สู่ตลาดจะต้องมาพร้อมกับการอัปสตรีมแพตช์ใน Linux, การสนับสนุน ABI/ABI-stability และการร่วมมือกับผู้ดูแลโปรเจ็กต์หลักเพื่อให้ไดรเวอร์และโมดูลถูกยอมรับในโค้ดหลัก ตัวอย่างเช่น การได้รับการยอมรับใน mainline kernel จะลดความเสี่ยงสำหรับผู้ให้บริการคลาวด์และผู้ผลิตอุปกรณ์ที่ไม่ต้องพึ่งแพตช์เฉพาะเจาะจง อีกทั้งการร่วมมือกับชุมชน AI จะช่วยให้ไลบรารีสำคัญ (เช่น BLAS, ONNX runtime) ถูกปรับให้รองรับคำสั่ง SIMD หรือเร่งฮาร์ดแวร์เฉพาะของ Arm ตั้งแต่ต้น

ผลต่อการออกแบบแพลตฟอร์ม เช่น reference designs, SDKs และ toolchains จะมีความชัดเจนและเป็นมาตรฐานมากขึ้น หาก Arm จัดหา reference platforms และชุดพัฒนา (SDK) ที่ครบถ้วน จะทำให้ผู้ผลิตฮาร์ดแวร์ (OEM/ODM) สามารถย่นระยะเวลา R&D ได้อย่างชัดเจน ตัวอย่างทางปฏิบัติได้แก่การปล่อย reference board พร้อมเฟิร์มแวร์ตัวอย่าง, board support packages (BSP), และชุดทดสอบที่ยืนยันความเข้ากันได้ของไดรเวอร์กับ Linux LTS kernel นอกจากนี้ การสนับสนุน toolchain อย่างเป็นทางการ (Arm Compiler, LLVM/Clang optimizations, GNU toolchain) และการเผยแพร่ profile การทำงานสำหรับโปรไฟล์ AI/ML จะช่วยให้ ISV ปรับโค้ดได้รวดเร็วและแม่นยำกว่าเดิม

ในแง่ของไลบรารีและสแตก AI มีความคาดหวังว่าผู้ให้บริการคลาวด์และผู้พัฒนาเฟรมเวิร์กจะร่วมมืออย่างใกล้ชิดกับ Arm เพื่อให้มีการเร่งฮาร์ดแวร์ (hardware acceleration) ที่ถูกเปิดเผยอย่างชัดเจน การยอมรับจากคลาวด์ผู้ให้บริการรายใหญ่ เช่น AWS ที่มีประสบการณ์กับ Graviton หรือผู้ให้บริการอื่น ๆ จะเป็นปัจจัยเร่งการยอมรับสำหรับลูกค้าองค์กร ทั้งนี้ รายงานและตัวอย่างจากตลาดชี้ให้เห็นว่าเครื่องมือและไลบรารีที่ปรับแต่งเฉพาะสามารถให้ประสิทธิภาพ/ค่าใช้จ่ายที่ดีกว่าถึงระดับหลักหลายสิบเปอร์เซ็นต์ในกรณีเฉพาะงาน

โอกาสสำหรับพาร์ทเนอร์ด้านซอฟต์แวร์และฮาร์ดแวร์ มีทั้งแบบระยะสั้นและระยะยาว พาร์ทเนอร์ซอฟต์แวร์สามารถนำเสนอซอฟต์แวร์ที่ปรับแต่งให้รองรับ Arm อย่างครบวงจร เช่น การเพิ่มการเร่งด้วย Neon/SVE, การปรับจูน JIT compiler, หรือการให้บริการสนับสนุนและรับรองความเข้ากันได้สำหรับลูกค้าองค์กร ด้านฮาร์ดแวร์ ผู้ผลิตโมดูลและบอร์ดสามารถใช้ reference designs ของ Arm เพื่อลดเวลาสู่ตลาด ขณะที่ผู้ให้บริการคลาวด์สามารถเพิ่มประเภทอินสแตนซ์ Arm เพื่อขยายตัวเลือกให้ลูกค้าและสร้างบริการจัดการสำหรับ workload ที่เหมาะสม

- การรับรองและการทดสอบ: พาร์ทเนอร์ควรเข้าร่วมกรอบการรับรองของ Arm เพื่อให้ไดรเวอร์และเฟิร์มแวร์ได้รับการทดสอบในระดับมาตรฐาน ลดความเสี่ยงในการนำไปใช้งานจริง

- การมีส่วนร่วมใน upstream: ส่งแพตช์และร่วมมือกับโครงการโอเพนซอร์สหลักเพื่อลดภาระการบำรุงรักษาพิเศษและยกระดับความเชื่อมั่นของลูกค้าองค์กร

- การสร้างเครื่องมือและ SDK เฉพาะ: พาร์ทเนอร์ซอฟต์แวร์สามารถพัฒนาชุดเครื่องมือ (profilers, debuggers, optimized libraries) ที่ตอบโจทย์ตลาดเฉพาะ เช่น edge, datacenter, mobile

- ความร่วมมือกับคลาวด์และ OEM: การทำพันธมิตรกับผู้ให้บริการคลาวด์และผู้ผลิตอุปกรณ์จะเป็นช่องทางสำคัญในการขยายการนำไปใช้จริง รวมทั้งการเสนอ managed services และ reference deployments

- โอกาสทางธุรกิจใหม่: ผู้ให้บริการจัดการระบบ, ผู้ให้คำปรึกษา, และ ISV สามารถสร้างบริการแยกย่อย เช่น การย้ายแอพ, การปรับจูนประสิทธิภาพ, และการรับรองความปลอดภัยสำหรับแพลตฟอร์ม Arm

สรุปได้ว่า การที่ Arm ผลิตชิปเองจะเร่งให้เกิดการเปลี่ยนแปลงในระบบนิเวศอย่างมีนัยสำคัญ ทั้งในด้านการร่วมมือกับชุมชนโอเพนซอร์ส การกำหนดมาตรฐานของ reference designs และการเปิดช่องทางใหม่ ๆ ให้กับพาร์ทเนอร์ซอฟต์แวร์และฮาร์ดแวร์ ผู้เล่นทุกฝ่ายจากเคอร์เนลไปจนถึงคลาวด์ต้องร่วมมือกันอย่างใกล้ชิดเพื่อให้แนวทางนี้สร้างคุณค่าเชิงเศรษฐกิจและเทคนิคที่มั่นคงต่อผู้ใช้และองค์กรในวงกว้าง

ซัพพลายเชนและการผลิต: Fabs, Capacity และต้นทุน

ซัพพลายเชนและการผลิต: Fabs, Capacity และต้นทุน

การที่ Arm พิจารณาขยายบทบาทสู่การผลิตชิปด้วยตัวเองหรือเพิ่มระดับการควบคุมซัพพลายเชน จะมีผลกระทบเชิงกลยุทธ์ต่อกำลังการผลิต (capacity) ต้นทุน และความเสี่ยงอย่างมีนัยสำคัญ ในเชิงปฏิบัติ Arm ต้องตัดสินใจระหว่างการเป็นผู้ผลิตโดยตรง (vertical integration) หรือการใช้ contract foundries รายใหญ่ เช่น TSMC, Samsung, และผู้ผลิตสัญญาอื่นๆ ซึ่งแต่ละทางเลือกมีข้อดีข้อเสียที่แตกต่างกันทั้งด้านต้นทุน การลงทุน และความยืดหยุ่นในการจัดส่ง

กำลังการผลิตที่เป็นไปได้และผู้ผลิตที่ Arm อาจเลือก — ในระยะสั้นและกลาง Arm มีแนวโน้มใช้ model ของการออกแบบแล้วจ้างผลิต (fabless + foundry) โดยจับมือกับ TSMC (ผู้นำตลาดสำหรับโหนดขั้นสูง มีส่วนแบ่งตลาดประมาณ 50–55% ในกลุ่ม foundry ปลายปี 2023–2024) และ Samsung Foundry เป็นคู่หลัก เนื่องจากทั้งสองรายมีเทคโนโลยี 5nm/3nm และความจุขั้นสูง นอกจากนี้ Arm อาจสำรองการผลิตกับ GlobalFoundries, UMC หรือ OSATs (Outsourced Semiconductor Assembly and Test) เช่น ASE/Amkor สำหรับการผลิตโหนดเก่า (e.g., 28nm, 14nm) และการแพ็กเกจจิ้ง เพื่อบริหารต้นทุนและความพร้อมจัดส่งทั่วโลก

ผลกระทบทางต้นทุนและความเสี่ยงจากการพึ่งพา foundry รายใหญ่ — การพึ่งพา TSMC/Samsung ช่วยให้ Arm ไม่ต้องรับภาระ CAPEX ขนาดใหญ่ (โรงงาน leading-edge หนึ่งแห่งอาจต้องใช้เงินลงทุนหลายพันล้านถึงหลักสิบพันล้านดอลลาร์) แต่ก็เปิดช่องให้เกิดความเสี่ยงด้าน capacity contention และการขึ้นราคาชั่วคราวในช่วงที่ความต้องการสูง ตัวอย่างเช่น ในช่วงวิกฤตชิปที่ผ่านมา lead time ของ foundry สามารถยืดออกเป็น 20–30 สัปดาห์หรือมากกว่า และต้นทุน NRE (non-recurring engineering) รวมถึงค่ามาสก์สำหรับโหนดขั้นสูงอาจสูงถึงหลักล้านดอลลาร์ต่อชิปเซ็ตหนึ่งรุ่น หาก Arm ต้องการการันตีปริมาณการผลิต อาจต้องซื้อสัญญา long-term capacity reservation ซึ่งมักมาพร้อมส่วนลดแต่ต้องผูกมัดทางการเงินและความเสี่ยงจากการเปลี่ยนเทคโนโลยี

กลยุทธ์ด้านการจัดหาและการสำรอง capacity — เพื่อบริหารความเสี่ยง Arm ควรใช้แนวทางผสมผสาน (hybrid strategy):

- ใช้ multi-sourcing ระหว่าง TSMC และ Samsung สำหรับโหนดขั้นสูง และมอบหมายการผลิตโหนดกลาง/เก่าให้ GlobalFoundries หรือ UMC เพื่อกระจายความเสี่ยง

- ทำสัญญาจองความจุระยะยาว (capacity reservation) สำหรับผลิตภัณฑ์สำคัญ พร้อมกับเงื่อนไขปรับปริมาณตามความต้องการ เพื่อแลกกับส่วนลดราคาและสิทธิ์เข้าใช้ไลน์ผลิตในช่วงขาดแคลน

- ลงทุนแบบเป็นพันธมิตร (joint ventures) กับ foundry หรือ OSAT ในการขยายไลน์ที่สำคัญ แทนการลงทุนสร้าง fabs ใหม่ด้วยตัวเอง ซึ่งช่วยลด CAPEX แต่ยังได้สิทธิ์พิเศษด้านการผลิต

- แยกสายผลิตตามตลาด — ใช้ผู้ผลิตในภูมิภาคเฉพาะสำหรับตลาดจีน/เอเชีย และใช้ผู้ผลิตสัญชาติอื่นสำหรับตลาดสหรัฐฯ/ยุโรป เพื่อลดความเสี่ยงด้านการเมืองและข้อจำกัดการส่งออก

การบริหารสต็อกและการจัดส่ง — ในสภาวะตลาดที่ผันผวน Arm จำเป็นต้องออกแบบนโยบายสต็อกที่สมดุลระหว่างการถือครองสินค้าสำรอง (safety stock) กับการหลีกเลี่ยงทุนฝังตัวสูง (working capital) กลยุทธ์ที่มักใช้ ได้แก่ vendor-managed inventory, consignment inventory กับลูกค้ารายใหญ่, และรองรับด้วยการผลิตแบบ staggered wafers เพื่อปรับแต่งให้ตรงกับความต้องการที่เปลี่ยนแปลง นอกจากนี้ การใช้บริการ OSAT ระดับโลกช่วยลดคอขวดด้านการแอสเซมบลีและทดสอบ ทำให้เวลา-to-market ดีขึ้นแม้ในช่วงที่ wafer capacity ตึงตัว

สรุปคือ หาก Arm ยังคงใช้โมเดลการออกแบบแล้วจ้างผลิต จะได้ประหยัดต้นทุน CAPEX และเข้าถึงเทคโนโลยีชั้นนำได้รวดเร็ว แต่ต้องแลกมาด้วยความเสี่ยงจากการพึ่งพา foundry รายใหญ่และความผันผวนของกำลังการผลิต ทางเลือกเชิงกลยุทธ์ที่สมเหตุสมผลสำหรับ Arm คือการกระจายซัพพลายเชนโดยผสานการสำรองความจุ การทำสัญญาระยะยาว และความร่วมมือเชิงกลยุทธ์กับผู้ผลิตและ OSATs เพื่อลดความเสี่ยง เพิ่มความยืดหยุ่นในการจัดส่ง และควบคุมต้นทุนในระยะยาว

ความหมายต่อยุค AI, Edge และ Data Center

ความหมายต่อยุค AI, Edge และ Data Center

การที่ Arm ประกาศจะออกแบบชิปของตนเองเป็นสัญญาณสำคัญที่อาจเปลี่ยนสมดุลของอุตสาหกรรมชิปเซมิคอนดักเตอร์ในยุคของ AI และ edge computing ได้อย่างชัดเจน โดยเฉพาะเมื่อผนวกกับความต้องการ NPU (Neural Processing Unit) และ accelerators สำหรับงาน inference ที่เพิ่มขึ้นอย่างรวดเร็วในอุปกรณ์พกพา อุปกรณ์ IoT และโซลูชัน edge อุตสาหกรรม การมีชิปของ Arm เองจะช่วยให้บริษัทสามารถนำเสนอ IP และสถาปัตยกรรมที่ปรับจูนสำหรับงาน AI ได้อย่างเป็นเอกภาพมากขึ้น ซึ่งอาจนำไปสู่ ประสิทธิภาพต่อพลังงาน (performance-per-watt) ที่ดีกว่าในหลายกรณี ซึ่งเป็นปัจจัยสำคัญสำหรับการใช้งานบน edge ที่จำกัดแบตเตอรี่และความร้อน

ในเชิงโอกาส ตลาด AI accelerators และ edge compute จะเปิดช่องทางแข่งขันใหม่ ๆ เมื่อ Arm เข้ามาเป็นผู้เล่นที่ออกแบบ SoC/accelerator เอง: ผู้ผลิตอุปกรณ์และผู้ให้บริการระบบสามารถเลือกใช้สถาปัตยกรรม Arm ที่มีการบูรณาการ NPU มาในตัวได้โดยตรง แทนที่จะพึ่งพา IP จากผู้ผลิตรายอื่นหรือต้องออกแบบ NPU แยกต่างหาก ซึ่งจะลดเวลาในการนำผลิตภัณฑ์สู่ตลาดและต้นทุนการบูรณาการ ตัวอย่างเช่น หาก Arm สามารถเสนอ IP NPU ที่ให้ประสิทธิภาพระดับหลาย TOPS (tera-operations per second) ในการบริโภคพลังงานเพียงไม่กี่วัตต์ บริบทของการประมวลผลแบบเรียลไทม์ (real-time inference) บนอุปกรณ์พกพาและกล้องวงจรปิดอัจฉริยะจะเปลี่ยนจากการส่งข้อมูลขึ้นคลาวด์เป็นการประมวลผลที่ขอบเครือข่ายได้มากขึ้น

ด้าน energy-efficiency ความได้เปรียบของการออกแบบที่รวม NPU/accelerator เข้ามาในชิป Arm ของตนเองคือการออกแบบฮาร์ดแวร์และแพ็กเกจซอฟต์แวร์ที่สอดคล้องกันมากขึ้น ส่งผลให้การจัดการพลังงาน (power management), การแบ่งโพรเซสระหว่าง CPU/NPU, และการทำงานร่วมกับโมเดล ML ถูกปรับแต่งอย่างเหมาะสม ผลลัพธ์ที่คาดหวังคือ อัตราพลังงานต่อการคำนวณที่ต่ำลง ซึ่งสำคัญสำหรับ use case เช่น inference แบบต่อเนื่องบนอุปกรณ์สวมใส่ กล้องรักษาความปลอดภัย หรือยานยนต์ ขณะเดียวกันยังช่วยลดปริมาณข้อมูลที่ต้องส่งกลับไปยัง data center (ลดแบนด์วิดท์และค่าใช้จ่าย) และเพิ่มความเป็นส่วนตัวของข้อมูลด้วยการประมวลผลบนอุปกรณ์

เปรียบเทียบในเชิงนโยบายการออกแบบกับกรณีศึกษาที่มีอยู่แล้ว: AWS Graviton และ Apple M-series ให้แนวทางที่เป็นประโยชน์ในการวิเคราะห์ — AWS Graviton แสดงให้เห็นว่า CPU ที่ออกแบบบนสถาปัตยกรรม Arm สามารถชิงส่วนแบ่งตลาดคลาวด์ได้ด้วยการให้ราคาต่อประสิทธิภาพที่ดีขึ้น (AWS รายงานผลปรับปรุง performance/price สำหรับ workload บางประเภทอยู่ในช่วงสองหลักหรือสูงกว่าในบางกรณี) แต่ Graviton เน้นไปที่ CPU และประสิทธิภาพของเวิร์กโหลดทั่วไปมากกว่าการเป็น NPU เฉพาะทาง ขณะที่ Apple M-series แสดงศักยภาพของการรวม NPU เข้ากับ SoC เพื่อประสิทธิภาพการเรียนรู้ของเครื่องบนอุปกรณ์ (on-device ML) ที่มีอัตราการใช้พลังงานต่ำ — Apple สามารถให้ inference แบบเรียลไทม์สำหรับฟีเจอร์หลายอย่างโดยไม่กระทบต่ออายุแบตเตอรี่ของผู้ใช้มากนัก

- โอกาสการแข่งในตลาด accelerators และ edge compute: Arm ที่ออกแบบชิปเองสามารถแข่งขันโดยเสนอ IP ที่พร้อมใช้งานสำหรับผู้ผลิต OEM/ODM และผู้ให้บริการระบบ นำไปสู่การแข่งขันด้านราคา การบูรณาการที่เร็วขึ้น และการเพิ่มจำนวนผู้เล่นในตลาด accelerator

- ข้อดีด้าน energy-efficiency สำหรับ edge และอุปกรณ์พกพา: การรวม NPU เข้ากับสถาปัตยกรรม Arm อาจปรับปรุงประสิทธิภาพต่อวัตต์อย่างมีนัยสำคัญ ซึ่งลดต้นทุนการดำเนินงานของอุปกรณ์ที่ต้องทำ inference ต่อเนื่องและยืดอายุแบตเตอรี่ของอุปกรณ์พกพา

- ผลกระทบต่อ data center และคลาวด์: ถ้า Arm นำเสนอชิปที่มีประสิทธิภาพด้าน ML ระดับสูงและการบริโภคพลังงานต่ำ ผู้ให้บริการคลาวด์อาจหันมาใช้ Arm-based servers ร่วมกับ accelerators แบบเฉพาะทางเพิ่มขึ้น ซึ่งจะกระตุ้นการแข่งขันกับ x86 ในบาง workload และเปลี่ยนโฟกัสของซอฟต์แวร์ให้รองรับสถาปัตยกรรม Arm มากขึ้น

สุดท้าย ผลลัพธ์จริงจะขึ้นกับสองปัจจัยสำคัญ: หนึ่งคือความสามารถของ Arm ในการออกแบบ NPU/accelerator ที่มี performance-per-watt และ latency ที่แข่งขันได้ในระดับสากล และสองคือความพร้อมของซอฟต์แวร์นิเวศ (compilers, frameworks, drivers) ที่จะทำให้ผู้ออกแบบระบบและนักพัฒนาสามารถย้ายหรือเร่งโมเดล AI ได้โดยไม่ต้องปรับเปลี่ยนมาก หาก Arm ประสบความสำเร็จทั้งสองด้าน เราอาจเห็นการเร่งตัวของนวัตกรรมทั้งในฝั่ง edge และ data center ตลอดจนการเปิดสนามแข่งขันใหม่ระหว่างผู้ผลิตชิปและผู้ให้บริการคลาวด์ ซึ่งจะเป็นประโยชน์ต่อผู้ใช้งานสุดท้ายจากความหลากหลายของโซลูชันและต้นทุนที่ต่ำลง

ความเสี่ยงเชิงกฎหมายและภูมิรัฐศาสตร์

ความเสี่ยงเชิงกฎหมายและภูมิรัฐศาสตร์

การที่ Arm ตัดสินใจเข้าสู่ตลาดการผลิตชิปด้วยตนเองจะเผชิญกับความเสี่ยงทางกฎหมายและภูมิรัฐศาสตร์ในหลายมิติ ซึ่งไม่เพียงส่งผลต่อการดำเนินงานเชิงพาณิชย์ แต่ยังเกี่ยวพันกับนโยบายความมั่นคงของรัฐและกรอบการควบคุมการส่งออกของประเทศชั้นนำ การประเมินความเสี่ยงเชิงนโยบายเหล่านี้เป็นเรื่องจำเป็นเมื่อพิจารณาว่าภาคเซมิคอนดักเตอร์เป็นส่วนสำคัญของห่วงโซ่อุปทานระดับโลก โดยตลาดรวมมีมูลค่าหลายร้อยพันล้านดอลลาร์ต่อปีและสถาปัตยกรรม Arm ถูกนำไปใช้ในอุปกรณ์พกพามากกว่า 90% ของโลก ซึ่งทำให้การเคลื่อนไหวของ Arm มีความหมายทางยุทธศาสตร์ทั้งในมิติเศรษฐกิจและความมั่นคง

ความท้าทายด้านการควบคุมการส่งออกและมาตรการจากรัฐบาล — ผู้เล่นในอุตสาหกรรมชิปต้องปฏิบัติตามกฎระเบียบการส่งออกที่เข้มงวด เช่น กฎหมายของสหรัฐฯ (Export Administration Regulations — EAR) รายการ Entity List และมาตรการควบคุมเทคโนโลยีที่อาจจำกัดการส่งออกเทคโนโลยีขั้นสูงไปยังบางประเทศ ตัวอย่างที่เห็นได้ชัดคือการจำกัดการส่งออกชิป AI และเทคโนโลยีการผลิตระดับหน้าสุดไปยังจีน ซึ่งส่งผลให้บริษัทต้องมีระบบตรวจสอบปลายทาง ผู้รับสินค้า และการขออนุญาตส่งออกที่ซับซ้อน การปฏิบัติผิดพลาดอาจนำไปสู่ค่าปรับทางแพ่ง/อาญา การถูกขึ้นบัญชีดำ และการสูญเสียสิทธิ์การเข้าถึงตลาดสำคัญ

ประเด็นการแข่งขันเชิงพาณิชย์และการตรวจสอบการผูกขาด — การที่ Arm เปลี่ยนบทบาทจากผู้ให้สถาปัตยกรรม/ไลเซนส์ไปสู่ผู้ผลิตชิปโดยตรง อาจกระตุ้นการสอบสวนจากหน่วยงานกฎการแข่งขันทั้งในสหรัฐฯ ยุโรป และเอเชีย เนื่องจากอาจเกิดความขัดแย้งทางผลประโยชน์กับลูกค้าที่เป็นผู้ผลิตชิปรายอื่น (fabless/IDM) ประเด็นที่ควรติดตามได้แก่การให้สิทธิ์ใช้งานแบบเลือกปฏิบัติ การตั้งราคาแบบกีดกัน การรวมแนวทางออกแบบกับผลิตภัณฑ์ของตนเอง และการใช้ข้อมูลจากลูกค้าเพื่อได้เปรียบเชิงพาณิชย์ กรณีศึกษาในอดีตของอุตสาหกรรมเซมิคอนดักเตอร์ เช่น การสอบสวนการกีดกันทางการค้าและการกำกับดูแลการควบรวมกิจการชี้ให้เห็นว่าการเคลื่อนไหวเชิงกลยุทธ์ของผู้เล่นรายใหญ่จะถูกจับตามองอย่างใกล้ชิด

แนวทางการจัดการความเสี่ยงทางกฎหมายสำหรับผู้เล่นในอุตสาหกรรม — เพื่อรับมือความเสี่ยงที่ซับซ้อน Arm และคู่แข่งควรพัฒนากลยุทธ์การปฏิบัติตามกฎหมายเชิงรุกและนโยบายภูมิรัฐศาสตร์ที่ชัดเจน ได้แก่

- การเสริมระบบคัดกรองการส่งออกและการปฏิบัติตามข้อกำหนด — ติดตั้งกระบวนการตรวจสอบลูกค้าและปลายทาง (end‑use/end‑user checks) จัดทำกระบวนการขออนุญาตส่งออก และฝึกอบรมพนักงานในเรื่อง EAR, Entity List และข้อจำกัดจากสหภาพยุโรป/สหราชอาณาจักร

- โครงสร้างการให้สิทธิ์ใช้งานและการแยกหน่วยธุรกิจ — พิจารณาโมเดลการให้สิทธิ์ (licensing) แบบโปร่งใส แยกสายงานการออกแบบและการผลิตเชิงพาณิชย์เพื่อบรรเทาความเสี่ยงการถูกสอบสวนผูกขาด และใช้มาตรการ Firewalls ภายในเพื่อป้องกันการใช้ข้อมูลลูกค้าอย่างไม่เป็นธรรม

- การมีส่วนร่วมเชิงรุกกับหน่วยงานกำกับดูแล — สื่อสารกับหน่วยงานการค้าและการแข่งขันในตลาดหลัก ตั้งคณะทำงานนโยบายสาธารณะ (public policy) เพื่อชี้แจงรูปแบบธุรกิจและข้อจำกัดทางเทคนิค ลดความไม่แน่นอนและป้องกันการตีความที่รุนแรงเกินไป

- กระจายห่วงโซ่อุปทานและพันธมิตรเชิงกลยุทธ์ — เพื่อบรรเทาความเสี่ยงจากมาตรการจำกัดการส่งออก ควรสร้างเครือข่ายผู้ผลิตและซัพพลายเชนในภูมิภาคต่าง ๆ (regionalization) และทำข้อตกลงร่วมทางเทคนิคกับพันธมิตรเพื่อลดการพึ่งพาจุดเดียว

- เตรียมแผนรับมือต่อการดำเนินคดีและการปรับแก้นโยบาย — จัดตั้งทีมกฎหมายระหว่างประเทศและที่ปรึกษาด้านการแข่งขันเพื่อรับมือการสอบสวนหรือคดีผูกขาด รวมถึงเตรียมแผนการยอมความและมาตรการเยียวยา (remediation) หากจำเป็น

สรุปคือ การขยายเข้าสู่การผลิตชิปของ Arm จะเพิ่มมิติด้านความเสี่ยงเชิงกฎหมายและภูมิรัฐศาสตร์อย่างมีนัยสำคัญ ทั้งนี้การป้องกันต้องอาศัยการผสานกันของมาตรการปฏิบัติตามกฎระเบียบ การออกแบบโครงสร้างธุรกิจที่ลดข้อขัดแย้ง และการมีส่วนร่วมกับภาครัฐอย่างต่อเนื่อง หากดำเนินการอย่างเป็นระบบ Arm และคู่แข่งสามารถลดความเสี่ยงเชิงนโยบายและรักษาการเข้าถึงตลาดสำคัญได้ แม้สภาพแวดล้อมทางภูมิรัฐศาสตร์จะทวีความซับซ้อนมากขึ้น

บทสรุป

การที่ Arm ประกาศเข้าสู่ธุรกิจผลิตชิปเองเป็นตัวเร่งสำคัญที่จะทำให้การแข่งขันในตลาดเซมิคอนดักเตอร์เข้มข้นขึ้นในหลายมิติ — ด้านเทคโนโลยี การออกแบบ (เช่น CPU, GPU, NPU และ IP ต่างๆ) ด้านต้นทุน และโดยเฉพาะอย่างยิ่งด้านระบบนิเวศของซอฟต์แวร์ที่อิงสถาปัตยกรรม Arm สถาปัตยกรรม Arm ถูกใช้อย่างแพร่หลายมากกว่า 90% ในสมาร์ทโฟนทั่วโลก และการขยายตัวสู่เซิร์ฟเวอร์และพีซีผ่านกรณีเช่น AWS Graviton (ที่ผู้ให้บริการอ้างว่าให้ผลประหยัดต้นทุนประมาณ 20–40%) และชิป Apple M-series ที่แสดงศักยภาพด้านประสิทธิภาพต่อกำลังไฟ ทำให้การที่ Arm ลงมาผลิตชิปเองจะกดดันให้ผู้ผลิตเดิม (รวมถึง Intel, AMD และกลุ่ม RISC‑V) ต้องปรับกลยุทธ์ ทั้งในแง่ราคาขาย การลงทุนวิจัยพัฒนา และการต่อยอดซอฟต์แวร์ให้รองรับนวัตกรรมใหม่ๆ

สำหรับผู้เล่นในอุตสาหกรรม แนวทางที่สำคัญเพื่อรักษาความสามารถในการแข่งขันคือการสร้างความร่วมมือเชิงกลยุทธ์ (partnerships กับผู้ผลิตชิปรายอื่น, ฟาวน์ดรี, และผู้พัฒนา IP), การประเมินและเสริมความแข็งแกร่งของซัพพลายเชน (ความเสี่ยงของกำลังการผลิต วัตถุดิบ และโลจิสติกส์) และการเร่งลงทุนในซอฟต์แวร์รองรับสถาปัตยกรรม Arm (เช่น คอมไพเลอร์ ระบบปฏิบัติการ ไลบรารี และเครื่องมือดีพลอย) เพราะการแข่งขันจะขยายตัวจากฮาร์ดแวร์สู่ชั้นซอฟต์แวร์ ซึ่งผู้ที่ลงทุนล่วงหน้าในการพอร์ตและเพิ่มมูลค่าทางซอฟต์แวร์จะได้เปรียบในระยะยาว มุมมองอนาคตชี้ว่าเราจะเห็นนวัตกรรมเร่งตัว การกดดันด้านราคา ตลาดอาจเกิดการรวมตัวหรือฟื้นตัวของพันธมิตรใหม่ๆ และโอกาสสำหรับผู้เล่นระดับกลางและรายย่อยที่เน้นซอฟต์แวร์หรือเฉพาะทางจะเพิ่มขึ้น แต่ทั้งนี้จะต้องเผชิญกับแรงกดดันทั้งจากการแข่งขันและการกำกับดูแลที่อาจเข้มงวดขึ้น

📰 แหล่งอ้างอิง: WIRED